BEDO DRAM

The abbreviation BEDO DRAM , short for English Burst Extended Data Out DRAM , means an electronic memory chip. This is a special variant of an Extended Data Out DRAM (EDO-DRAM), i. That is, a dynamic RAM (DRAM) in which the output data is present longer than normal and thus allows faster access to the next memory address.

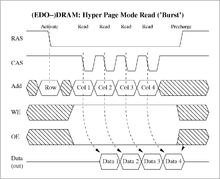

In contrast to the EDO DRAM internal control was at BEDO DRAM changed so that data in a so-called burst (dt. Approximately accumulation ) can be read, d. This means that after an address has been created, the subsequent memory address of a line can be read in just one clock cycle. For this purpose, the column and row address is applied for the first access as in normal DRAM with RAS ( Row Address Strobe , address strobe for the column) and CAS ( Column Address Strobe , address strobe for the column). However, only one CAS signal is used to access subsequent memory cells in the same row. The internal address counter is increased when the CAS signal is activated; this is referred to as burst mode and allows faster memory access to successive memory addresses.

Since only a few chipsets were supported, this technology could not establish itself on the market.

swell

- Rolf Klaus, Hans Käser: Fundamentals of computer technology. vdf Hochschulverlag AG, 1998, ISBN 978-3-7281-2475-3 , p. 85 .

- Axel Sikora: Paperback digital technology . Hanser Verlag, 2007, ISBN 978-3-446-40903-3 , p. 320 .

- Klaus Urbanski, Roland Woitowitz: Digital technology: a text and exercise book . Springer, 2004, ISBN 978-3-540-40180-3 , pp. 230-231 .

Individual evidence

- ↑ Thomas Flik: Microprocessor technology and computer structures . Springer, 2007, ISBN 978-3-540-26716-4 , pp. 695 .