Interrupt vector

The interrupt vector is in a computer system , the one program address to the occurrence of a hardware or software interrupt or an exceptional situation is bound. The Interrupt Service Routine (ISR) that answers the interrupt is located there. Each interrupt source has its own interrupt vector in order to be able to carry out the specific reaction to the interrupt with a different ISR. A special interrupt vector is the reset vector , which points to the first command to be executed after a reset .

Interrupt vector table

The location from which the interrupt vectors are read is different and precisely defined for each processor type. The vectors are usually stored in a table in the RAM memory , which allows greater flexibility in the manipulation of the jump addresses. But there are also processors in which the interrupt vectors are hard-wired (e.g. PICmicro ), or systems in which the vector is fetched from a peripheral module during the interrupt acknowledge cycle.

The interrupt vector table (IVT) of a larger operating system is a central structure that must be well protected against unauthorized access.

x86

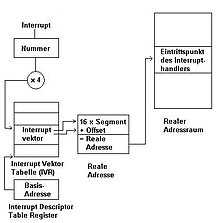

With the x86 processor, the interrupt vector table in real mode is usually at address 0x00000000 and has 256 entries of 32 bits each (CS, IP). To find the address of the interrupt handler it is looking for, the CPU only needs to multiply the interrupt number by 4 to obtain the offset to the base address. From the 4 bytes available there, it can then calculate the segment and offset address of the handler.

From the 80286 the CPU has its own register - IDTR (Interrupt Descriptor Table Register) - which contains the physical base address and length of the IVT. The IDTR is also used in real mode, so that a different position of the IVT is theoretically possible in real mode. For reasons of DOS compatibility, however, the IVT is usually not moved in real mode.

In the protected mode , the table can be placed anywhere in the address area and contains up to 256 interrupt descriptors which, in addition to the jump address, contain further information and priority specifications. In the event of unauthorized processor states or calculation errors, the exception vectors contained in the interrupt vector table are read and jumped to.

IA-32

The IA-32 has tables that depend on the operating mode. In real mode, in which the processor starts, this is from memory address 0x00000000 and has a length of 1024 bytes. The processor has a total of 256 interrupts and each vector is 4 bytes in size. A vector is made up of a segment address and an offset that are loaded into the CS and IP registers when called.

In protected mode, the interrupt table (which is called the interrupt descriptor table here) can be located anywhere in the memory. The position is specified or read out using the CPU commands LIDT and SIDT via the IDT register, in which the physical start address and the length of the table are specified. Each entry is 8 bytes, so the maximum size of the table is 2048 bytes. The entries differ from real mode because they are IA-32-specific descriptors. As a trap or interrupt gate, these point to a selector for a code segment, as well as contain an offset address for this segment or refer to a task status segment, a data structure in which the complete status of a program is stored (values for all registers, etc. ). The entries in the vector tables are called up via internal processor errors (entries 0 to 31) via an external connection that sends a vector number to the processor or by the software in the running program.

8080/8085 / Z80

There are 8 interrupts on these processors. The entry addresses are fixed and are calculated by multiplying the vector by 8 (i.e. 00 hex to 38 hex ). After a reset, the processors start executing the program at 00 hex , which corresponds to vector 0 at the same time. The interrupts can be called by an external request - the component then sends the corresponding opcode (C7 hex to FF hex ) to the processor.

The 8085 has the successor of 8080 an extended interrupt system. There are 3 external request lines that are directly linked to an entry address. These are 5.5, 6.5 and 7.5. The entry addresses are in the middle between the 8080 entry addresses: 5.5 to 2C hex , 6.5 to 34 hex and 7.5 to 3C hex .

The Z80 got an NMI (non maskable interrupt) as an extension of the 8080. Its entry address is fixed at 66 hex . After a reset, the processor is in an interrupt mode compatible with the 8080. Software can be used to switch to two other interrupt modes. In the IM1 mode, there is always a jump to vector 7 (38 hex ) for external interrupt requests . In mode IM2 a 256 byte long interrupt table with 128 entry addresses can be created. For this purpose, bits 15 to 8 of the start address of this table are entered in processor register I. The interrupt-triggering module then supplies bits 7 to 1. The processor then reads out the memory cell [100 hex × I + V] and [100 hex × I + V + 1], which represents the start address of the interrupt service routine.

68K

This processor supports 256 interrupts, the start addresses of which are stored in a table. The base address is stored in the vector base register, to which four times the interrupt number is then added.

Reset vector

The hardware reset is a special non-maskable interrupt that interrupts a running program and at the same time resets the registers . There is also a vector for him, the reset vector . It is the program address to which a jump is made after the power on reset or hardware reset. Since immediately after the reset, no RAM contents are available, the reset vector is always in read-only memory ROM stored in the system. For the 8086 this is the address FFFF: 0000, from the 80286 it is F000: FFF0. An intersegment jump command usually found at addresses FFFF0 ... FFFF4 leads to identical behavior in both processors.

C:\>debug -u f000:fff0 F000:FFF0 EA5BE000F0 JMP F000:E05B F000:FFF5 3033 XOR [BP+DI],DH F000:FFF7 2F DAS F000:FFF8 3137 XOR [BX],SI F000:FFFA 2F DAS F000:FFFB 3038 XOR [BX+SI],BH F000:FFFD 00FC ADD AH,BH F000:FFFF C430 LES SI,[BX+SI]

With other processors it is often the address 0 (0x0000).

various

An interrupt vector and an ISR must exist for each non-masked interrupt, otherwise an invalid address is jumped to when the interrupt occurs. Therefore, one of the first actions of the operating system after a reset is to build up the interrupt vector table and to install the interrupt service routines in order to then allow the interrupts ( interrupt enable flag ).