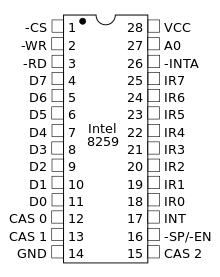

Intel 8259

The Intel 8259 is a programmable interrupt control block ( Programmable Interrupt Controller PIC), which primarily for Intel-8080 / 8085 processors has been developed. Later was chip together with the Intel 8086 / 8088 used and his successors. The component is mainly supplied in a 28-pin DIL housing . He was u. a. licensed to NEC and Siemens .

It has 8 interrupt inputs and one interrupt output. It has been used since the first PCs ( IBM-PC XT ). The inputs are connected to the interrupt pins of the devices in the system (keyboard, timer, printer, etc.), the output to the CPU.

use

The 8 inputs were soon no longer sufficient due to the growing number of devices in the system, and two modules were used instead. The output of one module ( slave ) is connected to an input of the other module ( master ) (usually at input # 2). The functionality of these two components is no longer implemented in separate chips on modern mainboards, but is integrated into the chipset.

The following sketch illustrates the cascading and shows an example assignment of the inputs:

PIC 1 (Master)

+--------------+ PIC 2 (Slave)

| IRQ 0 + <--- Timer +-------------+

| IRQ 1 + <--- Tastatur | IRQ 8 + <--- Echtzeituhr

| IRQ 2 +------------------+ | IRQ 9 + <--- ...

| IRQ 3 + <--- Seriell | | IRQ 10 + <--- ...

| IRQ 4 + <--- Seriell | | IRQ 11 + <--- ...

| IRQ 5 + <--- Soundkarte | | IRQ 12 + <--- PS/2 Maus

| IRQ 6 + <--- Floppy | | IRQ 13 + <--- Koprozessor

| IRQ 7 + <--- Parallel | | IRQ 14 + <--- Festplatte

+------+-------+ Port | | IRQ 15 + <--- Festplatte

| | +-----+-------+

| | |

| +--------------+

|

+--->>> Zur CPU

Most of the inputs are determined by the architecture of the PC and are not used by other devices, even if no corresponding device is available.

The interrupts are processed in a specific order that is determined by the input on the 8259. Normally input 0 has the highest priority, input 7 the lowest. This results in the following sequence: 0, 1, (2), 8, 9, 10, 11, 12, 13, 14, 15, 3, 4, 5, 6, 7. The IRQ numbering is specified by the mainboard: the 8259 adds the number of the input to a configurable value and then transfers this to the CPU. The numbering is usually carried out as indicated in the sketch.

The IRQ 2 itself is not used, it is the "pass-through" for the IRQs of the second 8259 (so-called cascade , this functionality is called cascading of the 8259).

The limited number of inputs, the inflexible and slow programming and, above all, the lack of multi-processor system support have led to the development of a successor, the APIC system. Although the PIC is still present alongside the APIC in current chipsets for reasons of compatibility, it is no longer used by modern operating systems.

Literature and data sheets

- Josef Koller: 16 bit microcomputer. 1st edition, Hofacker Verlag, Munich 1981, ISBN 3-921682-80-0 , chap. 4.2.1 "Interrupt controller 8259A", pp. 191–201.

- Martin Ernst, Andreas Stiller: PC components. Interrupts: The long way from a request to service. In: c't. No. 8, 1988, pp. 174-187.

- Microcomputer modules, data book 1979/80. Volume 3, Periphery, Siemens AG, order number B 2049, pp. 193–229.

- NEC Electronics (Europe) GmbH, 1982 Catalog, pp. 675-692.

- Intel Datasheet: 8259A Programmable Interrupt Controller (8259A / 8259A-2). ( bochs.sourceforge.net GZIP ; 257 kB).

Individual evidence

- ↑ Chemnitz University of Technology: The structure of the original IBM PC motherboard ( Memento of the original from December 8, 2011 in the Internet Archive ) Info: The archive link was automatically inserted and not yet checked. Please check the original and archive link according to the instructions and then remove this notice. .

- ↑ Chemnitz University of Technology: The AT motherboard ( Memento of the original from January 6, 2012 in the Internet Archive ) Info: The archive link was automatically inserted and not yet checked. Please check the original and archive link according to the instructions and then remove this notice. .