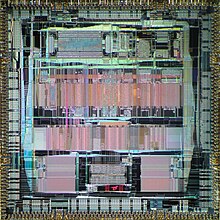

PA-RISC

Parallel / Precision Architecture Reduced Instruction Set Computer ( PA-RISC ) is a microprocessor architecture from Hewlett-Packard for use in servers and workstations . As is evident from the name, is a processor of RISC type transmission, the PA is short for Precision Architecture . It is also known under the name HP / PA for H ewlett P ackard P recision A rchitecture . The first processors were used in 1986, and production was finally discontinued in 2008. A few years earlier, HP began to use the Itanium or Itanium 2 processors developed together with Intel instead .

history

In the late 1980s, HP produced four lines of computers, each using different CISC processors. The PC-compatible HP Vectra series, introduced in 1986, was based on Intel 80286 processors. All other model series used CPUs from other manufacturers. The HP 200 series (1981) and HP 9000 300 series (1985) Unix ( HP-UX ) workstations were based on the Motorola 68k design. An additional 68k-based series was added in 1989 through the acquisition of Apollo , the later HP Apollo 9000 series 400 . The next independent series was the HP 300 series (1978), integrated multi-user computers based on a proprietary Silicon-on-Sapphire CPU design 8 (SoS design) and the Amigo / 300 operating system. The first series of the Hewlett-Packard 3000 series (1972) were also based on a SoS design and the MPE (operating system) . Finally, there was the HP 9000 Series 500 (1982) - minicomputers which the self-developed by HP 32- bit - FOCUS - CPU used. All non-Intel-based HP systems were consolidated into a uniform design from 1988 with the help of the new PA-RISC processor.

The first series of PA-RISC-7000 processors were designed for an address space of 32 bits and were initially used from March 1986 in the HP-3000 series for the models 930 and 950 and in the HP-9000 840s, which is identical to the 930.

A feature of the PA-RISC range is that most generations of these CPUs do not have a level 2 cache . Instead, large level 1 caches are used, initially connected as separate chips via a bus , and later integrated on a chip. Only the PA-7100LC, PA-7200 and PA-7300LC had an L2 cache. Another innovation in the PA-RISC design were the additional so-called multimedia instructions ( SIMD ), which were introduced for the first time with the PA-7100LC. As of the PA-7200, the external MMC / SMC memory controller was also used; for the first time, it enables a 36-bit address space (with the K420 max. 8 GB, otherwise max. 32 GB main memory) on which the 32-bit versions can also use from HP-UX version 11.00 or higher via “ Memory Windows ” (compare PAE or AWE ).

In 1994 the PA-RISC-2.0 specification , which is still valid today, was defined, which provides a word length of 64 bits and thus enables a linear address space that is larger than 4 GB. Further changes concerned the pipeline architecture and the division of the instruction cache into two units, one for instructions that are processed quickly, one for those that are more time-consuming. The first representative of the new standard was the PA-8000.

Production of the PA-RISC processors was originally supposed to end in 2004, but was expanded due to various delays in Itanium development. The production of new systems based on the HP-PA processor architecture ended on December 31, 2008. The IA-64 architecture (Itanium) developed by HP together with Intel since the late 1990s is used as the successor .

The PA-RISC processors are supported by NetBSD , OpenBSD or Linux , among others . Since the release of Debian 3.0 (Woody), HPPA is an officially supported Debian architecture, the current stable distribution of Debian-HPPA GNU / Linux is version 6.0. It was released on February 6, 2011. Also Gentoo Linux supports HPPA. An Ubuntu port also existed up to release 9.04 (“Jaunty”). Since release 9.10 there is no further Ubuntu support for PA-RISC processors. In general, the HPPA ports have become quiet.

Model history

Web links

- Specifications PA-RISC 2.0

- The OpenPA project engl. With a lot of information and images of various PA-RISC based systems. (Also non HP) With a section about free operating systems on PA-RISC HP9000 machines.

Individual evidence

- ↑ http://hpmuseum.net/display_item.php?hw=836

- ↑ http://www.netbsd.org/ports/hp700/

- ↑ http://www.openbsd.org/hppa.html

- ↑ http://parisc-linux.org

- ↑ http://www.debian.org/ports/hppa/

- ↑ Debian 6.0 "Squeeze" released. In: debian.org. Software in the Public Interest, Inc., February 6, 2011, accessed February 8, 2011 .

- ↑ http://www.gentoo.org/doc/en/handbook/handbook-hppa.xml