Zilog Z280: Difference between revisions

m Dating maintenance tags: {{Notability}} {{Mergeto}} |

declining merge. This chip is more different from the Z80 than many other upcs that have their own articles, like the 65C02. |

||

| Line 1: | Line 1: | ||

{{notability|date=August 2023}} |

{{notability|date=August 2023}} |

||

{{mergeto|Zilog Z80|date=August 2023}} |

|||

{{Short description|16-bit microprocessor by Zilog}} |

{{Short description|16-bit microprocessor by Zilog}} |

||

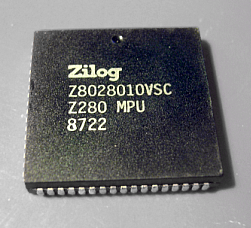

[[File:Z280 PLCC 1987.png|thumb|right|251px|The Z280 in a [[Plastic leaded chip carrier|PLCC68]] package]] |

[[File:Z280 PLCC 1987.png|thumb|right|251px|The Z280 in a [[Plastic leaded chip carrier|PLCC68]] package]] |

||

| Line 70: | Line 69: | ||

[[Category:Zilog microprocessors]] |

[[Category:Zilog microprocessors]] |

||

[[Category:16-bit microprocessors]] |

[[Category:16-bit microprocessors]] |

||

{{microcompu-stub}} |

{{microcompu-stub}} |

||

Latest revision as of 13:44, 2 September 2023

The topic of this article may not meet Wikipedia's general notability guideline. (August 2023) |

The Zilog Z280 is a 16-bit microprocessor, an enhancement of the Zilog Z80 architecture, introduced in July 1987. It is basically the Z800, renamed, with slight improvements such as being fabricated in CMOS.[1] It was a commercial failure. Zilog added a memory management unit (MMU) to expand the addressing range to 16 MB, features for multitasking and multiprocessor and coprocessor configurations, and 256 bytes of on-chip static RAM, configurable as either a cache for instructions and/or data, or as part of the ordinary address space. It has a huge number of new instructions and addressing modes giving a total of over 2000 combinations. It is capable of efficiently handling 32-bit data operations including hardware multiply, divide, and sign extension. It offers Supervisor and User operating modes, and optionally separate address spaces for instructions and data in both modes (four total possible address spaces). Its internal clock signal can be configured to run at 1, 2 or 4 times the external clock's speed (e.g. a 12MHz CPU with a 3 MHz bus). Unlike the Z80 the Z280 uses a multiplexed arrangement for its address and data busses. More successful extensions of the Z80-architecture include the Hitachi HD64180 in 1986 and Zilog eZ80 in 2001, among others. See further Zilog Z800.

The Z280 had many advanced features for its time, most of them never seen again on a Zilog processor:[2]

- On-chip instruction and/or data cache, or on-chip RAM

- Instruction pipelining

- High performance 16-bit Z-BUS interface or 8-bit Z80-compatible bus interface

- Built-in MMU with memory protection

- Ability to determine which register set is in context with instructions JAF and JAR

- Three on-chip 16-bit counter/timers

- Four on-chip DMA channels

- On-chip full duplex UART

- User I/O trap

- Supervisor mode (privileged instructions)

- Illegal instruction trap[citation needed]

- Coprocessor emulation trap

- Burst mode memory access

- Multiprocessor support, with many bus configuration modes

- Support for multiple external coprocessors through an accelerated communication interface

- Multiple I/O pages, which also allows for internal I/O devices without restricting the address range of the I/O ports like on eZ80, or conflicting with existing motherboard devices, like the Z180.

- Stack overflow warning

References[edit]

- ^ EDN November 27, 1986 p133

- ^ Z280 MPU Microprocessor Unit Preliminary Technical Manual (PDF). San Jose, California: Zilog. 1989. Archived from the original (PDF) on 2019-09-11. Retrieved 2009-07-15.

- Z80 Family Data Book. San Jose, California: Zilog. January 1989.

- Reh, Tilmann (1991-09-16). "The CPU280 and Z280". TCJ. Retrieved 2009-07-15.

Further reading[edit]

- Harston, J.G. (1998-04-15). "Full Z280 Opcode List". Retrieved 2009-07-15.