Damascene process

The Damascene process , like its further development, is the Dual Damascene process , a manufacturing process from semiconductor technology . It is mainly used in integrated circuits ( microchips ) with copper conductor tracks. The name "Damascene" comes from an ancient decoration technique , the inking (also Damascene , English damascening ), in which a material is introduced into previously made recesses.

background

Until the early 2000s, aluminum was the only conductor material used in semiconductor manufacture . For the production of metallization levels (consisting of a structured layer for the intermediate contacts and a further layer with the actual conductor tracks), the aluminum was first applied over the entire surface and then structured using dry etching processes . Since there is no comparable etching process available for copper, this procedure could not be adopted when some companies switched to copper technology at the beginning of the 2000s, in which aluminum as a conductor path material was replaced by copper.

The damascene process or its further development, the dual damascene process, was developed as an alternative manufacturing process . In contrast to the damascene process, in the dual damascene process the VIAs ( vertical interconnect access , contact connections between two metallization levels) and the overlying metallization level are filled with copper in one process step. This means that only one copper CMP step is necessary, in which the copper that protrudes after galvanic deposition is leveled.

Procedure

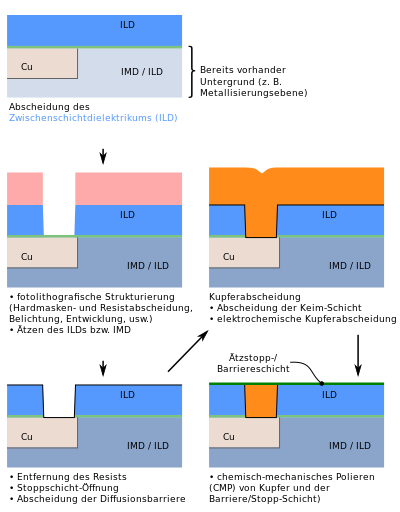

Starting from an existing substrate, for example silicon or already deposited metallization levels, an insulation layer ( dielectric ), often silicon dioxide (SiO 2 ) , is first deposited over the entire area. This is followed by a photolithographic structuring, i.e. a photoresist is applied and structured. The structured photoresist layer now present serves as a mask for the subsequent dry etching process, with which the later contact holes (vias) or conductor tracks are etched. The etching ends on the dielectric copper diffusion barrier (for example silicon nitride ) located under the dielectric , which serves as an etch stop layer. After the etching, the photoresist residue is removed.

After this structuring, the etched trenches are filled with an electrically conductive material such as copper or tungsten (actually only in the first metallization level with contact to the silicon substrate). Since copper easily diffuses into the dielectric ( inter metal dielectric , IMD, or inter layer dielectric , ILD), it is necessary to apply a diffusion barrier before the copper is deposited. This diffusion barrier must be electrically conductive, since the barrier is also applied to the bottom of the vias, that is to say to the contact point between two metallization levels. In addition, the thickness of the barrier layer reduces the effective diameter of the via holes and thus increases their electrical resistance. An electrically conductive barrier is also cheaper to minimize this effect.

The copper deposition itself can take place either via electrochemical deposition or metal-organic chemical vapor deposition (MOCVD). Both processes are again carried out over the entire area, and the trenches are also “overfilled”, this is to ensure that no cavities are created in the next metallization level; the electrical contact would then not be ensured or would have a higher resistance. The excess copper is then removed by chemical mechanical polishing (CMP) and leveled.

Finally, a barrier layer is deposited again, as otherwise the copper could easily diffuse into higher levels. Since the barrier layer is again deposited over the entire surface and not further structured, it must consist of a non-conductive material (e.g. silicon nitride). Otherwise short circuits could arise between the conductor tracks of a metallization level. Unlike aluminum, however, it does not form a protective oxide. The barrier layer therefore also serves as a passivation layer , i.e. it protects the copper from the environment. This is necessary because copper is easily oxidized and the electrical resistance would increase to a higher level of metallization. The copper oxide is permeable to water and oxygen, so that over time the copper would continue to oxidize, making the conductor tracks unusable. In addition, the barrier layer serves as an etch stop for a subsequent Damascene process.

Current developments

If the structures are reduced further, copper interconnects are unsuitable, since copper only has good conductivity in large structures. In small structures and films, its resistance increases comparatively early. The reason is that copper does not get its conductivity from a large number of free charge carriers, but from their large free path, which is disturbed in small structures and films. Substances like rhodium, iridium, ruthenium, cobalt, nickel and aluminum then conduct electricity better than copper or silver.

literature

- Shyam P. Murarka, Moshe Eizenberg, Ashok K. Sinha (Eds.): Interlayer Dielectrics for Semiconductor Technologies . Elsevier / Academic Press, Amsterdam et al. 2004, ISBN 0-12-511221-1 , pp. 218 ff .

Web links

- Phillipp Laube: copper technology. In: semiconductor.org. October 20, 2009. Retrieved November 24, 2009 .