Second level address translation

Second Level Address Translation ( SLAT ), also known as nested paging , is a hardware-supported virtualization technology that allows more efficient implementation of shadow page tables compared to a software-based virtualization solution . AMD first implemented SLAT through a technology called Rapid Virtualization Indexing (RVI) by AMD and has supported this in its processors since the introduction of the third Opteron processor generation (code name Barcelona) in 2007. With the Nehalem processor family, Intel introduced an implementation of SLAT in 2008, which Intel itself calls Extended Page Tables (EPT). It is supported in certain processors of the Core i7 , Core i5 and Core i3 class.

overview

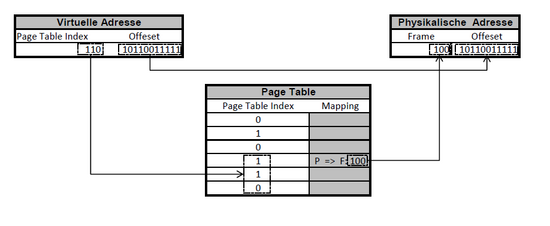

Modern processors differentiate between the concepts of physical and virtual memory with regard to memory management. Application processes only access the virtual memory. These accesses are implemented by the processor or the memory management unit (MMU) as a component of the processor from the virtual to the physical address space. The processor saves the assignment in so-called Page Tables or Translation Lookaside Buffers (TLB). The term “virtual memory” has nothing to do with the memory of virtual machines, but is a concept that is already used in modern x86 processors, regardless of virtualization, and is used by all modern operating systems.

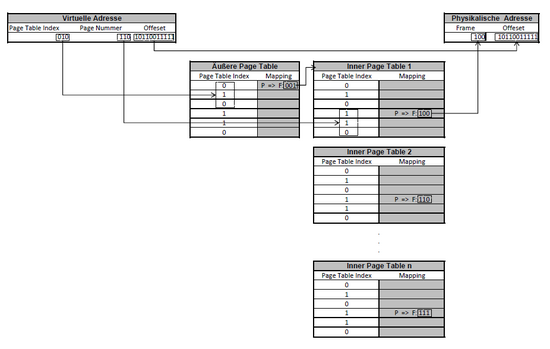

Since such page tables can become very large due to the large memory of modern systems, the concept was expanded to a multi-level page table lookup in which several levels of page tables are used. This means that page tables that are not required can be stored more easily in external storage and, in general, it is easier to deal with large address spaces.

If the hypervisor and several virtual machines are added to this concept, another address translation is required. This further address translation takes place between the memory calls of the virtual machine and the memory areas assigned to the hypervisor. If there is no hardware support for this, the hypervisor must carry out this implementation in order to then address the memory via the MMU and the multi-level mechanism mentioned above. This double implementation led to significant performance losses when operating virtual machines compared to operating directly on the hardware.

The processor manufacturers recognized this performance potential and expanded the already multi-stage page table mapping process to include additional stages that do the mapping for the virtualization. This technology is called "Second Level Address Translation" (SLAT for short) due to the further stages of mapping for virtualization. Compared to the software-based solution as described above, it was hoped that this would result in considerable performance gains for virtualization.

If SLAT and multi-level page table mapping are used together, the number of mapping levels to be run through doubled with the same address size of the physical guest address and the virtual guest address and the same size of the page tables. This fact makes caching mechanisms for the intermediate levels of host and guest page tables very important, since not all tables can always be kept in memory and the access times can still be kept short through clever caching. It is therefore sensible to choose large page table sizes for the host page tables in order to reduce the number of page table levels required.

Implementations

Extended Page Tables

Extended Page Tables (EPT) is a second generation x86 virtualization technology for the Memory Management Unit (MMU). It is supported in certain processors of the Core i7 , Core i5 , and Core i3 class, among others .

With the Westmere series of processors, Intel added a feature that allows logical processors to be started directly in "real mode". The feature is called "Unrestricted Guest" by Intel and requires the EPT feature. According to a VMWare article: "EPT provides performance gains of up to 48% for MMU-intensive benchmarks and up to 600% for MMU-intensive microbenchmarks", i. H. According to VMWare, EPT can achieve performance increases of between 48% and 600%, although these measurements depend very much on the use cases on which the tests were based. VMWare found out that virtualization using EPT can in certain borderline cases even be slower than using a software-based method of the hypervisor.

Rapid Virtualization Indexing

AMD Opteron CPUs from the 0x10 Barcelona Line and Phenom II CPUs and subsequent processor generations support an advanced virtualization technology, which AMD calls "Rapid Virtualization Indexing" (during development it was called "Nested Page Tables") and the SLAT is implemented.

In a VMware research paper it was shown that RVI can achieve up to 42% performance gain compared to the software-based implementation. Tests carried out by Red Hat showed a doubling of the performance for OLTP benchmark tests.

Hypervisor support

The following hypervisors support SLAT:

- Hyper-V for Windows Server 2008 R2 , Windows 8 and later versions. Windows 8 Hyper-V requires SLAT or EPT.

- KVM 2.6.26 and later versions

- VirtualBox 2.0.0 and later versions

- VMware ESX / ESXi 3.5 and later versions

- Xen 3.2.0 and later versions

- bhyve supports and requires EPT

It should be noted that some hypervisors require processors that support EPT or RVI as they no longer support software-based page table mapping themselves. The list is not up to date in this regard.

See also

Web links

- Method and system for a second level address translation in a virtual machine environment (patent)

- Second Level Address Translation Benefits in Hyper-V R2

- Virtualization in Linux KVM + QEMU (PDF)

Individual evidence

- ^ Matt Gillespie, Best Practices for Paravirtualization Enhancements from Intel Virtualization Technology: EPT and VT-d . In: Intel Software Network . Intel. November 12, 2007. Retrieved July 6, 2008.

- ↑ AMD with information on "Barcelona" . ( planet3dnow.de [accessed on June 28, 2017]).

- ↑ Gil Neiger, A. Santoni, F. Leung et al: Intel Virtualization Technology: Hardware Support for Efficient Processor Virtualization Archived from the original on September 25, 2012. In: Intel (Ed.): Intel Technology Journal . 10, No. 3, September, pp. 167-178. doi : 10.1535 / itj.1003.01 . Retrieved July 6, 2008.

- ^ First the Tick, Now the Tock: Next Generation Intel Microarchitecture (Nehalem) . (PDF) In: Intel (Ed.): White Paper Intel . September. Retrieved July 6, 2008.

- ↑ Technology Brief: Intel Microarchitecture Nehalem Virtualization Technology (PDF) Intel. March 25, 2009. Retrieved November 3, 2009.

- ↑ Intel® Virtualization Technology List . Ark.intel.com. Retrieved February 17, 2014.

- ↑ http://2013.asiabsdcon.org/papers/abc2013-P5A-paper.pdf : "Intel added unrestricted guest mode on Westmere micro-architecture and later Intel CPUs, it uses EPT to translate guest physical address access to host physical address . With this mode, VMEnter without enable paging is allowed. "

- ↑ http://download.intel.com/products/processor/manual/326019.pdf : "If the“ unrestricted guest ”VM-execution control is 1, the“ enable EPT ”VM-execution control must also be 1"

- ↑ Performance Evaluation of Intel EPT Hardware Assist

- ↑ Rapid Virtualization Indexing with Windows Server 2008 R2 Hyper-V | The Virtualization Blog . Blogs.amd.com. March 23, 2009. Retrieved May 16, 2010.

- ↑ AMD-V Nested Paging . July 2008. Archived from the original on September 5, 2012. Retrieved on December 11, 2013.

- ↑ a b Performance Evaluation of AMD RVI Hardware Assist (PDF) Archived from the original on February 26, 2015. Retrieved on May 16, 2010.

- ↑ Red Hat Magazine | Red Hat Enterprise Linux 5.1 utilizes nested paging on AMD Barcelona Processor to improve performance of virtualized guests . Magazine.redhat.com. November 20, 2007. Retrieved May 16, 2010.

- ↑ AMD-V Rapid Virtualization Indexing and Windows Server 2008 R2 Hyper-V Second Level Address Translation . Doing IT Virtual. Retrieved May 16, 2010.

- ↑ Ed Bott: Does your PC have what it takes to run Windows 8's Hyper-V? . ZDNet. December 8, 2011. Retrieved February 17, 2014.

- ↑ AMD Processors with Rapid Virtualization Indexing Required to Run Hyper-V in Windows 8

- ↑ Kernel Newbies: Linux 2 6 26 . Retrieved September 2, 2014.

- ↑ Sheng Yang: Extending KVM with new Intel Virtualization technology (PDF) In: linux-kvm.org . KVM forum. June 12, 2008. Archived from the original on March 27, 2014. Info: The archive link was automatically inserted and not yet checked. Please check the original and archive link according to the instructions and then remove this notice. Retrieved March 17, 2013.

- ↑ Changelog for VirtualBox 2.0 . Archived from the original on October 22, 2014. Info: The archive link was automatically inserted and not yet checked. Please check the original and archive link according to the instructions and then remove this notice. Retrieved September 2, 2014.

- ↑ Benchmarks: Xen 3.2.0 on AMD Quad-Core Opteron with RVI . June 15, 2008. Retrieved May 13, 2011.

- ↑ Implementation of a BIOS emulation support for BHyVe: A BSD Hypervisor