Zilog Z280: Difference between revisions

Stub |

m robot Adding: it:Zilog Z280 |

||

| Line 52: | Line 52: | ||

[[Category:Zilog microprocessors]] |

[[Category:Zilog microprocessors]] |

||

| ⚫ | |||

[[it:Zilog Z280]] |

|||

[[ja:Z280]] |

[[ja:Z280]] |

||

[[pl:Zilog Z280]] |

[[pl:Zilog Z280]] |

||

| Line 57: | Line 60: | ||

[[ru:Zilog Z280]] |

[[ru:Zilog Z280]] |

||

[[sv:Zilog Z280]] |

[[sv:Zilog Z280]] |

||

| ⚫ | |||

Revision as of 22:41, 4 September 2009

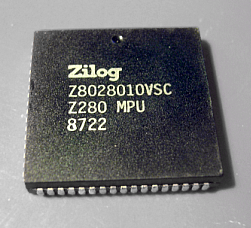

The Zilog Z280 was an enhancement of the Zilog Z80 architecture introduced in July 1987, basically a slightly improved CMOS version of the earlier NMOS Zilog Z800, both versions were commercial failures. They added a memory management unit (MMU) to expand the addressing range to 16 MB, features for multitasking and multiprocessor and coprocessor configurations, a 256 byte cache, and a huge number of new instructions and addressing modes (giving a total of over 2000 combinations). Its internal clock signal ran at 2 or 4 times the external clock's speed (e.g. a 16MHz CPU with a 4MHz bus). Later, more successful, enhancements to the Z80-architecture include Hitachi HD64180 and Zilog eZ80, among others. See further Zilog Z800.

Notes

This article includes a list of general references, but it lacks sufficient corresponding inline citations. (July 2009) |

References

- Z280 MPU Microprocessor Unit Preliminary Technical Manual (pdf). San Jose, California: Zilog. 1989. Retrieved 2009-07-15. (Note: 20MB pdf file)

- Z80 Family Data Book. San Jose, California: Zilog. 1989.

{{cite book}}: Unknown parameter|month=ignored (help) - Reh, Tilmann (1991-09-16). "The CPU280 and Z280". TCJ. Retrieved 2009-07-15.

Further reading

- Harston, J.G. (1998-04-15). "Full Z280 Opcode List". Retrieved 2009-07-15.

This article is based on material taken from the Free On-line Dictionary of Computing prior to 1 November 2008 and incorporated under the "relicensing" terms of the GFDL, version 1.3 or later.