NOR flash

NOR flash refers to a type of flash memory that consists of NOR gates . NOR memory was developed as a flexible replacement for EPROM , PROM and ROM memories . NOR flash is a classic address - and data - port addressed and can be used without additional glue logic one to the bus system controller are connected.

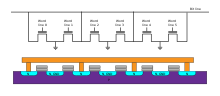

construction

While all bytes can be accessed randomly with read access, with write access it must be taken into account that the bytes are grouped into blocks. Although the individual bytes can be written to independently of one another, only a transition of the bits from 1 to 0 is possible here. However, only complete blocks can be deleted. All bits in the bytes are set to 1 again. Depending on the block type used, access to other blocks is also possible during the delete process, which takes a multiple of the read access time. The granularity of the block size is usually 64 KiB - however, it varies from component to component and sometimes also within a component: Some Flash ROMs have the lower (bottom boot) or upper (top boot) memory requirements for applications with boot code ) Storage area blocks with a smaller size.

Possess NOR Flash's technology-related, with the same structure size smaller storage capacities than NAND Flash's because their memory cells more space on the demand. NOR flash memories are usually completely error-free on delivery - in contrast to NAND flash memories, where defective memory blocks up to a certain number per chip are common. NOR flash cells are usually designed for several 100,000 write and erase cycles.

Areas of application

NOR flashes are mainly used to store boot code or the firmware of a computer system.

advantages

- linearly addressable memory, enables code execution (execute in place)

- high writing speed for small amounts of data

- Problem-free coupling to controller systems due to the SRAM- like bus system

disadvantage

- relatively high power consumption

- slow when writing and deleting large amounts of data

- only available for relatively small storage capacities (maximum 64 gigabits (May 2019))