Bus (data processing)

A bus is a system for data transmission between several participants via a common transmission path . If a momentary data transfer takes place between two participants, the other participants must be silent at the same time, otherwise they would disturb. The speaking authorization time is distributed according to a (time or signal) scheme known to all participants. Listening is not restricted. Colloquially - often for historical reasons - data transmission systems that actually have a different topology are sometimes referred to as “buses” .

etymology

There are various explanations for the origin and original meaning of the word “bus”.

- In the absence of written sources, an interpretation of the term is based on the memories of engineers who worked with BUS systems in the 1970s and earlier. The term comes from the abbreviation “BU” used in circuit diagrams for B ack (mounted) Panel U nit , which is used to describe a component in 19-inch racks that is mounted on the rear wall of the slide-in unit. BUS then denotes B ack Panel U nit S ockets for slots mounted on the back wall. Accordingly, the English term busbar is derived , which means something like busbar.

- Occasionally a connection with the omnibus is assumed for the origin of the term .

- Sometimes theories about backronymes were also expressed. The abbreviation bus stands for Binary Unit System .

Basic concepts

Earlier buses were actually just parallel power rails with multiple connections. The English names omnibus bar and bus bar for such busbars ( power rail ) originate from this time (from 1898 ). The term bus for busbars is common in the electrical systems of aircraft to this day, whereby a distinction is made primarily between AC bus (alternating voltage) and DC bus. This designation was probably adopted for data collecting lines (data buses) that pass on information to the connected participants.

Several communicating components can be connected to the signal wires on which information can be transmitted (possibly synchronized). The components connected to a bus are also referred to as nodes or bus participants .

Parallel and serial

It can basically parallel of serial different buses:

In the case of a serial bus, the information to be transmitted is broken down into its smallest units (e.g. individual bits ). These are sent one after the other over just one signal line.

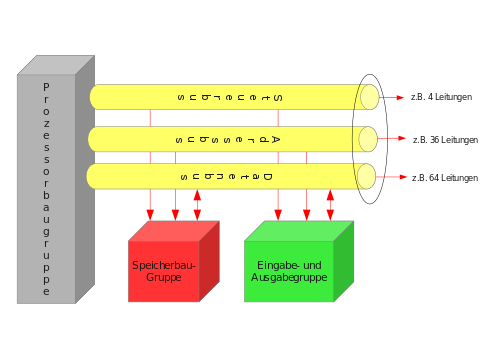

In a parallel bus there are multiple signal lines, e.g. B. 8, so that an information packet (here e.g. 1 byte ) can always be sent at the same time. The signal lines must stay in the same cycle and have the same signal transit times; their common course threatens crosstalk .

A parallel bus essentially consists of a number of signal cores running next to one another, on which information can be transmitted in a synchronized manner and to which several components are connected. The number of lines running next to each other is also called the width of the bus - it is generally equal to the number of bits that a bus can transmit at the same time.

Master and slave, initiator and target

Nodes that are allowed to independently initiate a communication process on the bus (send unsolicited data to other nodes) are called active nodes or masters , otherwise they are called passive nodes or slaves - such nodes are only allowed to respond to requests.

A bus that allows multiple master nodes is called a multimaster bus . In the case of a multi-master bus, a central or decentralized bus switch is necessary, which ensures that only one master has control of the bus at any given time. This is necessary because simultaneous write accesses to the bus can not only lose data but also damage the hardware. With a central bus switch, bus access is controlled by a special component called a bus arbiter . The node that initiates access to the bus is called the initiator , the target of such (read or write) access is called the target . Some buses offer a separate signal line for the slave nodes, on which a slave can send the master a signal bit that a slave would like to be queried.

Usage type

Depending on the type of use, a distinction is made between system buses , memory buses , peripheral buses and input / output buses .

Bus structures

Signal reflection and termination

Whether something is functionally / signal-wise a bus does not necessarily depend on the physical topology .

Since very high-frequency electrical signals are often transmitted on bus systems, reflections occurring at the branches and ends of the transmission medium cannot be neglected; they can lead to the cancellation of the signals through interference at certain points and thus to the malfunction of the entire system. For this reason, an essentially one-dimensional electrical conductor as a transmission medium is favorable in terms of signal technology and is found most frequently ( e.g. SCSI ). Here reflections at the line ends can easily be prevented by termination. Termination by a simple terminating resistor causes high power dissipation, an alternative RC element causes a fluctuating quiescent level. The active termination, which specifies the quiescent level through a voltage regulator, is more complex.

Multiplexing

Since address and data buses require a large number of identical conductor tracks on a printed circuit board , on the one hand this takes up a lot of space and requires a corresponding number of pins on the components, on the other hand this can also increase electrical problems such as crosstalk . One solution is therefore to cut this number in half by dividing the information into two halves: the more significant bits and the less significant bits. These two groups are sent one after the other in two bus phases : one half is sent and the other half of the signals over the same lines ( multiplex bus ). An additional control pin must then identify these bus phases. It is therefore a time division multiplex method . That was in practice z. This is done, for example, with the address bus of the 8080 processor, and with dynamic RAMs ( DRAMs ) this leads to the RAS and CAS cycles .

Bus as part of the computer

In computer architecture, a bus is a subsystem that transfers data or energy between computer components within a computer or between different computers. Unlike a terminal in which a device with a connected other via one or more lines ( Point-to-point connection ), a Bus several peripherals over the same set of wires together.

Modern computer buses can be used both in parallel and bit-serial. While in the actual network topology of the classic bus line, all participants hang next to one another on the bus, nodes can be connected in a chain-like arrangement using suitable contacts. In addition to the network topology on the physical level, a bus-like behavior can also be simulated by appropriate implementations (see higher transmission levels in the OSI model ).

Most computers have internal and external buses. An internal bus connects internal components of a computer to the motherboard , for example the connection between the CPU and the main memory. Such an internal bus is also known as a local bus because it is intended to connect devices that are present in the computer itself and not with devices in other computers or with external ones. An external bus accordingly connects external peripherals to the main board.

For historical reasons, internal connection systems that do not have a topological bus structure are sometimes referred to as “bus systems” - mostly because the previous systems were topologically still real bus systems. For example, PCIe is often referred to as a bus system ( PCI was a real bus), although topologically it is a point-to-point system.

Addressing method

A bus system is always organized in such a way that only one single node outputs data to the bus at a certain point in time (or problems with simultaneous writing are solved). In the vast majority of cases, the data should be transported to a certain other node and processed by this. (Only in rare cases do several receiving nodes use the sent data at the same time, for example with the CAN buses of an automobile or with broadcast messages). Addressing is performed to identify the destination node, often via the address bus set up specifically for this purpose .

Buses differ in the way that individual nodes are addressed. There are a number of typical practices for both parallel and serial buses.

Addressing in parallel bus systems

A simple addressing scheme is as follows: only one component is a bus master (usually this is the processor), all the others are passive. For each connected slave there is a select line via which the master declares this slave to be its communication partner. The actual data is then sent via a separate data bus. This method is used, for example, in SPI .

If each connected component has its own address decoder, a "slave device number" can be transmitted instead of separate select lines, for which only lines are required. The individual address decoders then use the device number to decide independently of one another whether or not their component is the one intended. This method is used, for example, with the ISA or XT bus. Example: For n = 32 possible devices, only 5 address lines would be necessary instead of 32 select lines, because 2 5 = 32.

Another principle works without its own address lines. In accordance with the multiplexing described above, the address is first transmitted over the lines. Addressing can now take place (as described above) using an address decoder, for example - the partners involved now have to remember whether they are being addressed, since the lines are used for other purposes after the end of the address phase - for data transmission - and thus the address is no longer used is available on the bus. Normally there is a separate control line that shows whether an address or a data word is currently on the signal lines. This method is used, for example, with the I²C or PCI bus.

A modification of this is used with the SCSI bus. Before addressing (called the selection phase in SCSI jargon ) there is an arbitration phase. Each component that wants to use the bus reports by assigning '1' to the data line that corresponds to its address (SCSI ID) . This limits the number of possible addresses to the number of parallel bus lines (compared to the non-multiplexed address bus with lines), but a bus conflict can be avoided quite easily, i.e. the situation where several components want to use the bus at the same time: With SCSI has the device with the highest address has the highest priority and now becomes the bus master (initiator).

The methods described can also be combined with one another. In addition, it should be noted that real bus topologies are usually far more complex than those assumed here. In a computer system, different bus types are usually connected to a bus hierarchy , which differ in the type of addressing and which are linked to one another via bridges. Such bridges are able to translate the addressing from one bus protocol into the other. Special addressing aspects of multimaster buses were also not taken into account here.

Addressing in serial bus systems

The data transmitted on serial buses can be viewed as data packets (or telegrams ) that are divided into several fields. A data packet contains at least the recipient address and the data to be transmitted. Connected components look at the recipient field and then decide whether to process or discard the packet.

Bus mastering

Bus mastering means that the processor of a computer system temporarily transfers control of the bus to an adapter card , the so-called bus master. This bus master then independently addresses memory and IO areas for the purpose of data transfer . The bus master operates as a kind of bridge or as an independent CPU. While such a secondary processor dominates the peripheral bus, the CPU is usually able to carry out other work in the system , provided that the necessary resources are accessible . Most of the time, the bus to the memory is still partially usable, so there is time sharing. In modern multitasking operating systems in particular, this has a positive effect on the ability to react, with bus master activity often being linked to the operating system via an interrupt signal. The purpose of the adapter card is to serve certain tasks asynchronously to other tasks.

If bus mastering is not limited to buses on the CPU of a computer, there are other methods of bus arbiting in the area of computer networks:

- When token passing, the active bus master holds a so-called token , which is nothing more than a memory variable ( flag ). Once he has completed his transmission, he forwards this token to a specific neighbor on the bus (in the computer network). This is mainly used in ring buses. If you are not physically dealing with a ring bus, it is a matter of software to bring the potential bus participants into a well-defined order known to everyone.

- Other buses (example: CAN or Ethernet ) are prepared from the outset so that collisions between several participants attempting to send at the same time can occur. It is then their additional task to recognize such collisions ( collision detection ) and to react sensibly. It is part of the definition of the respective bus or computer network to determine the latter strategy. It is obvious that such a method can also be used for wireless radio links, and it is used accordingly.

historical development

First generation

Memories and other devices have been attached to the bus at the same addresses and data pins that the CPU itself uses, with parallel connections. The communication was controlled by the CPU which reads the data from the devices and the blocks from the memory. Everything was clocked by a central timer that controlled the operating speed of the CPU. Connected devices indicated to the CPU that they were about to send or receive data by sending a signal on other CPU pins, usually through some form of interrupt . For example, a drive controller (see Controller ) signaled to the CPU that new data was ready to be read, whereupon the CPU moved the data by reading the memory on the port that corresponded to the drive . Almost all early computers were put together this way, starting with the S-100 bus in the Altair and going through to the IBM PC in the 1980s.

However, this “first generation” of bus systems suffered from the serious disadvantage that everything on the bus works at the same speed and all devices had to share a single clock . Increasing the speed of the CPU was not easy because you had to increase the speed of all connected devices as well. This led to the strange situation that very fast CPUs had to be throttled in order to be able to communicate with other devices in the computer. Another problem was that the CPU was required for all operations and so when it was busy with other tasks the real data throughput of the bus suffered drastically. Another practical problem was that these early bus systems were difficult to put together because they required many jumpers to set the various operating parameters.

Second generation

"Second generation" bus systems such as NuBus were aimed at solving some of these problems. They usually divided the computer into two “worlds”, the CPU and memory on one side and the devices to be connected on the other, with a bus controller in between. This made it possible to increase the speed of the CPU without affecting the bus. It also reduced much of the burden of moving data out of the CPU and into the cards and controller, because devices could talk to each other over the bus without turning on the CPU. This resulted in much better actual performance in practice, but also required much more complexity in the equipment installed in the computer. These bus systems also tackled the speed problem by simply choosing a larger data transport route, moving from the 8-bit parallel buses of the first generation to 16 or 32-bit in the second. Another improvement was the addition of software settings that reduced or replaced the number of jumpers.

Nonetheless, the newer systems had one negative characteristic that they shared with their earlier cousins: everything attached to the bus (except the CPU) had to work at the same speed. Since the CPU was now isolated and its speed could be increased without problems, the operating speed of the CPUs and the memory increased continuously much faster than that of the bus systems with which they worked together. The result was that bus speeds were now much slower than necessary for a modern system, and the machines were hungry for data because they worked much faster than data could be moved back and forth. A particularly typical example of this problem was that video cards quickly outstripped even the newer bus systems such as PCI . For example, the bus concept was deviated from for graphics cards and an exclusive, significantly faster connection (port) was introduced for the graphics card, the Accelerated Graphics Port (AGP). The next step and state of the art in this development at the end of 2005 is PEG, PCI Express for Graphics with 16 lanes.

During this period, an increasing number of external devices also began to use their own bus systems. When the drives were first introduced, they were connected to the bus with a plug-in card. This is why computers have so many bus-connected slots . In the 1980s and 1990s, new systems like SCSI and ATA were introduced as a result, and most of the slots in modern systems remained empty. Today there are five different bus systems in a typical PC to operate the various devices.

Later on, the concept of the local bus was preferred to the external bus. The former refers to bus systems designed to work with internal devices such as graphics cards , and the latter to connect external devices such as scanners . This definition was always imprecise: IDE is an external bus in terms of its type of use; but it will almost always be found within the computer.

Third generation

"Third generation" buses are now on the rise, including HyperTransport and InfiniBand . They usually run at the very high speeds needed to support memory and video cards, while lower speeds are possible to support communication with slower devices such as drives. They are also very flexible in terms of their physical connections and can be used both as internal buses and to connect different computers to one another.

This can lead to complicated problems when it comes to serving different requests, which means that the software comes to the fore compared to the actual hardware design . In general, third generation buses tend to look more like a network than a bus (in the traditional understanding), with more protocol information requirements than previous systems, and the ability for different devices to use the bus simultaneously.

Bus systems

Data bus

A data bus transfers data between components within a computer or between different computers. Unlike a connector where one device is connected to another device by one or more lines, a bus can connect multiple peripheral devices together using the same set of lines. In contrast to the address bus or control bus, the data bus is bidirectional (apart from the address bus in DMA mode).

The terms 4-bit, 8-bit, 16-bit, 32-bit or 64-bit CPU usually refer to the width of the internal data path of such a CPU, which is normally connected to the (general purpose) register - and processing width of the ALU match. The internal data path is usually just as wide as the external data bus. The Intel i8088 CPU, for example, is an exception . Here the internal data path is 16 bits wide, while the external data bus is only 8 bits wide. Graphics cards also have higher bus widths to increase processing speed.

The designation as data bus is used in several contexts:

- with an emphasis on data : to distinguish it from common connections, such as the power supply

- with an emphasis on bus : to distinguish the topology, such as B. direct point-to-point connections

- with parallel buses: to differentiate between address and control lines

Address bus

In contrast to the data bus, an address bus is a bus that only transfers memory addresses . The bus width, i.e. the number of connecting lines, determines how much memory can be addressed directly. If an address bus has n address lines, memory locations can be addressed directly. In a bus with 32 address lines, bytes (one memory cell = 8 bits ) = 4 Gibibytes (GiB) can be addressed. With a 64-bit address bus, bytes = 16 Exbibytes (EiB) can even be addressed. As a rule, the address bus of a 64-bit architecture is not physically implemented in this width (see above under multiplexing ). The specification 64-bit bus refers more to the width of the data bus. However, 64-bit data can be interpreted as the address of another memory location ( indirect addressing ).

This bus is unidirectional and is controlled by the respective bus master (see above). The latter is usually the CPU, but DMA- capable blocks in particular can also take over this bus when they become active. With 8- and 16-bit processor architectures, the address bus is often wider than the architecture width (example: 80286 : 16-bit architecture with 24-bit address bus); 32-bit architectures sometimes also have a wider address bus. In the case of 64-bit architectures, the address bus is usually smaller (44–52 bit) than the architecture width.

Control bus (control bus)

The control bus (unidirectional) is a part of the bus system (bidirectional), said controller (English control ) achieved the bus system. These include the lines for read / write control (direction on the data bus), interrupt control, bus access control, timing (if a bus cycle is required), reset and status lines. Which of the lines are used in a bus depends on the type and structure of the bus. In multi-master systems in which more than one subsystem can take over bus control, an arbiter is required as a decision-making authority.

CPU internal bus

The internal CPU bus is used for communication between the internal units of the processor (between control unit, arithmetic unit and their registers), if necessary also with the L1 cache.

CPU-external bus

The external CPU bus connects processor (s), (L2-) cache, memory and peripheral bus interface, also called front side bus (FSB), or alternatively only with the chipset (or its northbridge ) where those external elements are connected.

Computer-internal buses

These buses connect components within a computer, for example the CPU with the graphics card and with various input / output components.

Computer-external buses

These buses connect the computer to external peripheral devices . Only those interfaces are meant here that really have a bus character, i.e. allow the connection of several external devices at the same time, for example the SCSI bus .

Areas of application

Bus systems are used in particular within computers and for connecting computers with peripheral devices , but also in the control of machines (field buses).

In automobiles , bus systems are used to connect the individual electronic system components of a vehicle . This measure is intended to increase the failure and interference immunity. In addition, other electronic systems can be integrated more easily and it is easier to update new software . A bus system also makes it possible to convert a vehicle into a “mobile office”.

Bus systems are also being used more and more frequently in building technology, e.g. B. the European installation bus (EIB). The bus system can be used to control lighting , window and door monitoring, heating , air conditioning and other devices in a building. The installation of a bus system should be taken into account when planning the building, as the system, especially the necessary cables and lines, requires a lot of space. Subsequent installation could involve considerable structural measures.

Since the mid-1990s, bus systems have also become increasingly common in building and door communication. These systems mostly operate independently of the rest of the building automation and are therefore often found in residential buildings with a lower standard. Advantages compared to conventional door intercoms are the significantly smaller wiring and installation effort, simplified troubleshooting and easy expandability of the entire system. Existing conventional systems can be easily converted.

See also

literature

- Werner Kriesel ; Tilo Heimbold ; Dietmar Telschow: Bus technologies for automation - networking, selection and application of communication systems (with CD-ROM). Hüthig Verlag, Heidelberg 1998, 2nd edition 2000, ISBN 3-7785-2778-9 .

- Franz-Josef Lintermann, Udo Schaefer, Walter Schulte-Göcking, Klaas Gettner: Simple IT systems. Textbook / specialist book . 5, 1st corrected reprint edition. Bildungsverlag EINS, 2008, ISBN 978-3-8237-1140-7 , p. 57-61 .

- Werner Zimmermann and Ralf Schmidgall: Bus systems in vehicle technology - protocols, standards and software architecture. 5th edition, Springer Vieweg, 2014, ISBN 978-3-658-02418-5 .

Web links

Individual evidence

- ↑ a b IEC 60050 - International Electrotechnical Vocabulary - Details for IEV number 351-56-10. International Electrotechnical Commission, accessed January 31, 2014 .

- ↑ a b Bernhard Huber, Georg Schnurer: SCSI 1-2-3 - Paths through the SCSI jungle, c't - magazine for computer technology 11/1993, p. 106 ff., Online archive at heise.de/artikel- archive (chargeable)

- ↑ "Bus systems in automobiles" Elaboration on the seminar lecture by Daniel Schüller (PDF; 532 kB) University of Koblenz, accessed on January 16, 2013

- ↑ Bus systems for building automation - daylight - building technology , construction network knowledge, accessed on January 16, 2013