A NOR gate (from English : n ot or - not or , or from English nor - (neither -) nor; also called Peirce function after Charles S. Peirce ) is a logic gate with two or more inputs A, B, ... and an output Y, between which there is a logical NOT OR link . A NOR gate outputs 1 (w) when all inputs are 0 (f). In all other cases, i. H. if at least one input is 1, a 0 is output.

The literature uses the following notations for the NOR operation of variables A and B :

A.

NOR

B.

A.

↓

B.

¬

(

A.

∨

B.

)

A.

∨

¯

B.

A.

∨

B.

¯

A.

+

B.

¯

A.

+

¯

B.

¬

(

A.

+

B.

)

{\ displaystyle A \, \ operatorname {NOR} \, B \ qquad A \ downarrow B \ qquad \ neg \ left (A \ lor B \ right) \ qquad A \; \; \! \! {\ overline {\ lor}} \; \; \! \! B \ qquad {\ overline {A \ lor B}} \ qquad {\ overline {A + B}} \ qquad A \; \; \! \! {\ overline { +}} \; \; \! \! B \ qquad \ neg \ left (A + B \ right)}

Overview

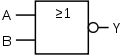

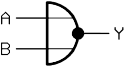

function

Circuit symbol

Truth table

Relay logic

IEC 60617-12

US ANSI 91-1984

DIN 40700 (before 1976)

Y

=

A.

∨

B.

¯

{\ displaystyle Y = {\ overline {A \ vee B}}}

Y

=

A.

∨

¯

B.

{\ displaystyle Y = A \; \; \! \! {\ overline {\ vee}} \; \; \! \! B}

Y

=

A.

+

B.

¯

{\ displaystyle Y = {\ overline {A + B}}}

Y

=

A.

↓

B.

{\ displaystyle Y = A \ downarrow B}

Y

=

A.

∖

B.

{\ displaystyle Y = A \ backslash B}

A.

B.

Y = A ⊽ B

0

0

1

0

1

0

1

0

0

1

1

0

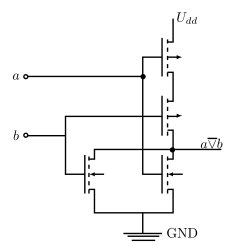

realization The electronic implementation takes place, for example (with positive logic ) with two (or correspondingly more) switches ( transistors ) connected in parallel , which connect output Q to ground (logic 0) as soon as one of them is switched on. If all are off, the ground connection is interrupted and the output Q is at positive potential (logical 1).

Functional principle of a NOR gate

Q

=

x

NOR

y

{\ displaystyle Q = x \, \ operatorname {NOR} \, y}

Realization of a NOR gate in CMOS technology (unfavorable to implement, since the two PMOS transistors are connected in series and are already more high-resistance than NMOS transistors with the same chip area )

a

∨

¯

b

=

a

NOR

b

{\ displaystyle a \; \; \! \! {\ overline {\ lor}} \; \; \! \! b = a \, \ operatorname {NOR} \, b}

Logic synthesis According to the following logical equivalence , a NOR operation can also be built up from NAND gates alone :

x

∨

¯

y

=

[

(

x

∧

¯

x

)

∧

¯

(

y

∧

¯

y

)

]

∧

¯

[

(

x

∧

¯

x

)

∧

¯

(

y

∧

¯

y

)

]

{\ displaystyle x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y = \ left [\ left (x \; \; \! \! {\ overline {\ land}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ land}} \; \; \! \! \ left (y \; \; \! \ ! {\ overline {\ land}} \; \; \! \! y \ right) \ right] \; \; \! \! {\ overline {\ land}} \; \; \! \! \ left [\ left (x \; \; \! \! {\ overline {\ land}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ land}} \ ; \; \! \! \ left (y \; \; \! \! {\ overline {\ land}} \; \; \! \! y \ right) \ right]}

Logical links and their implementation using NOR gates:

With the Peirce function alone, all two-valued truth functions can be represented, i.e. every Boolean function is equivalent to a formula that only contains the NOR function. Because of this property of functional completeness , the peirce function is called a basis of the two-digit logical functions (another basis is the NAND function).

NOT ( negation , not)

x

¯

{\ displaystyle {\ overline {x}}}

≡

{\ displaystyle \ equiv}

x

∨

¯

x

{\ displaystyle x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x}

AND ( conjunction , and)

x

∧

y

{\ displaystyle x \ land y}

≡

{\ displaystyle \ equiv}

(

x

∨

¯

x

)

∨

¯

(

y

∨

¯

y

)

{\ displaystyle \ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor} } \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right)}

NAND (not-and)

x

∧

¯

y

{\ displaystyle x {\ overline {\ land}} y}

≡

{\ displaystyle \ equiv}

[

(

x

∨

¯

x

)

∨

¯

(

y

∨

¯

y

)

]

∨

¯

[

(

x

∨

¯

x

)

∨

¯

(

y

∨

¯

y

)

]

{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \ right] \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \ right]}

OR ( disjunction , or)

x

∨

y

{\ displaystyle x \ lor y}

≡

{\ displaystyle \ equiv}

(

x

∨

¯

y

)

∨

¯

(

x

∨

¯

y

)

{\ displaystyle \ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline {\ lor} } \; \; \! \! \ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right)}

NOR (not-or)

x

∨

¯

y

{\ displaystyle x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y}

≡

{\ displaystyle \ equiv}

x

∨

¯

y

{\ displaystyle x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y}

XOR (Exclusive-Or)

x

∨

_

y

{\ displaystyle x \; \; \! \! {\ underline {\ lor}} \; \; \! \! y}

≡

{\ displaystyle \ equiv}

(

x

∨

¯

y

)

∨

¯

[

(

x

∨

¯

x

)

∨

¯

(

y

∨

¯

y

)

]

{\ displaystyle \ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline {\ lor} } \; \; \! \! \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \ right]}

XNOR (Exclusive-Not-Or)

x

∨

_

¯

y

{\ displaystyle x \; \; \! \! {\ overline {\ underline {\ lor}}} \; \; \! \! y}

≡

{\ displaystyle \ equiv}

[

(

x

∨

¯

y

)

∨

¯

x

]

∨

¯

[

(

x

∨

¯

y

)

∨

¯

y

]

{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! x \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right]}

implication

x

→

y

{\ displaystyle x \ rightarrow y}

≡

{\ displaystyle \ equiv}

[

(

x

∨

¯

x

)

∨

¯

y

]

∨

¯

[

(

x

∨

¯

x

)

∨

¯

y

]

{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! y \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right]}

x

←

y

{\ displaystyle x \ leftarrow y}

≡

{\ displaystyle \ equiv}

[

x

∨

¯

(

y

∨

¯

y

)

]

∨

¯

[

x

∨

¯

(

y

∨

¯

y

)

]

{\ displaystyle \ left [x \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor} } \; \; \! \! y \ right) \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [x \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \ right]}

equivalence

x

↔

y

{\ displaystyle x \ leftrightarrow y}

≡

{\ displaystyle \ equiv}

[

(

x

∨

¯

y

)

∨

¯

x

]

∨

¯

[

(

x

∨

¯

y

)

∨

¯

y

]

{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! x \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right]}

Verum (always true)

⊤

{\ displaystyle \ top}

≡

{\ displaystyle \ equiv}

[

(

x

∨

¯

x

)

∨

¯

x

]

∨

¯

[

(

x

∨

¯

x

)

∨

¯

x

]

{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! x \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right]}

Falsum (always wrong)

⊥

{\ displaystyle \ bot}

≡

{\ displaystyle \ equiv}

(

x

∨

¯

x

)

∨

¯

x

{\ displaystyle \ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor} } \; \; \! \! x}

literature Ulrich Tietze, Christoph Schenk: Semiconductor circuit technology . 12th edition. Springer, 2002, ISBN 3-540-42849-6 .

<img src="https://de.wikipedia.org/wiki/Special:CentralAutoLogin/start?type=1x1" alt="" title="" width="1" height="1" style="border: none; position: absolute;">

![{\ displaystyle x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y = \ left [\ left (x \; \; \! \! {\ overline {\ land}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ land}} \; \; \! \! \ left (y \; \; \! \ ! {\ overline {\ land}} \; \; \! \! y \ right) \ right] \; \; \! \! {\ overline {\ land}} \; \; \! \! \ left [\ left (x \; \; \! \! {\ overline {\ land}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ land}} \ ; \; \! \! \ left (y \; \; \! \! {\ overline {\ land}} \; \; \! \! y \ right) \ right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e2642ed86ad26c40f62a73174b2d4500cf70a3f4)

![{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \ right] \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \ right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8a032944b997e45f0ce6171c05da5b7783d83a65)

![{\ displaystyle \ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline {\ lor} } \; \; \! \! \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \ right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/49b4ad8ad27bc07ffed74d84eed2072c2f799a74)

![{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! x \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e8c117475eaba2ecf4c7f2adea4bebf1e525a96b)

![{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! y \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/64246548bf1a94c3c2f6490953a91dc07cd601f1)

![{\ displaystyle \ left [x \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor} } \; \; \! \! y \ right) \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [x \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left (y \; \; \! \! {\ overline {\ lor}} \; \; \! \! y \ right) \ right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/20a00fde266312e48345b62a7b693864fe081588)

![{\ displaystyle \ left [\ left (x \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline { \ lor}} \; \; \! \! x \ right] \; \; \! \! {\ overline {\ lor}} \; \; \! \! \ left [\ left (x \; \ ; \! \! {\ overline {\ lor}} \; \; \! \! x \ right) \; \; \! \! {\ overline {\ lor}} \; \; \! \! x \ right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e3506cc35653f587edeb5991975bd09732839edc)