NAND gate

| Gate types | |

|---|---|

| NOT | |

| AND | NAND |

| OR | NOR |

| XOR | XNOR |

A NAND gate (from English : n ot and - not and ) is a logic gate with two or more inputs A, B, ... and an output Y, between which there is a logical NOT AND link . A NAND gate outputs 0 when all inputs are 1. In all other cases, i. i.e., if at least one input is 0, a 1 is output.

Overview

| function | Circuit symbol | Truth table | Relay logic | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US ANSI 91-1984 | DIN 40700 (before 1976) | ||||||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||

The spelling corresponds to Sheffer's stroke .

use

NAND gates play the role of a standard module in digital technology , since they alone can be used to assemble all logical links and thus also more complex circuits (such as adders , multiplexers , etc.), see also complete logic systems .

| shortcut | implementation |

|---|---|

NOT x

|

x NAND x

|

x AND y

|

(x NAND y) NAND (x NAND y)

|

x NAND y

|

x NAND y

|

x OR y

|

(x NAND x) NAND (y NAND y)

|

x NOR y

|

((x NAND x) NAND (y NAND y)) NAND ((x NAND x) NAND (y NAND y))

|

x XOR y

|

(x NAND (y NAND y)) NAND ((x NAND x) NAND y)

|

((x NAND y) NAND y) NAND ((x NAND y) NAND x)

|

|

x XNOR y

|

(x NAND y) NAND ((x NAND x) NAND (y NAND y))

|

| ≡ x ⇔ y | |

| x ⇒ y |

x NAND (y NAND y)

|

| x ⇐ y |

(x NAND x) NAND y

|

| x ⇔ y |

(x NAND y) NAND ((x NAND x) NAND (y NAND y))

|

| ≡ x XNOR y | |

| verum |

(x NAND x) NAND x

|

| falsum |

((x NAND x) NAND x) NAND ((x NAND x) NAND x)

|

realization

The circuitry is implemented, for example, with two (or correspondingly more) switches ( transistors ) connected in series , which connect output Q to ground (logic 0) when they are all switched on. If one of them is off, the ground connection is interrupted and the output Q is at positive potential (logical 1).

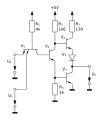

The NAND standard component in transistor-transistor logic (TTL), a well-known digital IC as a quadruple NAND gate with the designation 7400 , uses a single transistor with several emitters at the input instead of several transistors. These special transistors are also known as multiemitter transistors . The previous logic , the Diode-Transistor-Logic (DTL), uses several input diodes instead of the multi-emitter transistor for linking.

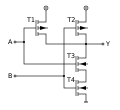

In the NMOS logic , a NAND gate with three equivalent n-channel MOS field effect transistors (n-MOSFETs) can be implemented with less chip area. The equivalent function is also available in CMOS logic with four MOSFETs with lower power: If there is high potential at inputs A and B, T3 and T4 conduct, T1 and T2 block. This means that there is low potential at output Y. With all other input states there is high potential at the output, because T1 and / or T2 are conducting and at the same time T3 and / or T4 are blocking.

- Circuit implementation of NAND gates in different logics:

literature

- Erwin Böhmer, Dietmar Ehrhardt, Wolfgang Oberschelp: Elements of applied electronics: Compendium for training and work. 16th edition, Vieweg & Teubner Verlag, Wiesbaden 2010, ISBN 978-3-8348-0543-0 , pp. 240–242.

- Detlef Kamke: Digital Electronics: An Introduction for Physicists. Teubner Verlag, Wiesbaden 1985, ISBN 978-3-519-03077-5 , pp. 33-35.

Web links

- Gates (symbols according to IEC 60617-12) (PDF, accessed on September 17, 2015)

- Digital circuit technology (PDF, accessed on September 17, 2015)

- Propositional Logic and Gates (PDF, accessed September 17, 2015)