AND gate

| Gate types | |

|---|---|

| NOT | |

| AND | NAND |

| OR | NOR |

| XOR | XNOR |

An AND gate is a gate with several inputs and one output, where the output delivers a 1 if 1 is present at all inputs. It corresponds to the logical AND . In switching algebra , the AND operation is represented by • (Mal), & or ∧ and is also referred to as a conjunction .

Overview

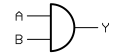

| function | Circuit symbol | Truth table | Relay logic | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US ANSI 91-1984 | DIN 40700 (before 1976) | ||||||||||||||||||

|

|

|

|

||||||||||||||||||

AND gates with a larger number of inputs

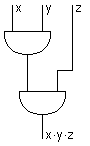

An AND gate has two inputs (AND 2 ) as standard , but AND gates with more than two inputs are also available in stores. The figure below shows an AND gate with three inputs (AND 3 ).

Including a circuit for an AND gate with three inputs, which was implemented from 2 gates with 2 inputs each. AND gates with even more inputs can be constructed in a corresponding manner.

Even if the circuit symbol hardly provides any information about the internal structure, in the case of gate families for which both types of representation are used, the lower one can be interpreted as an indication of less favorable runtime behavior.

An AND gate can be used, for example, to control a machine: The machine should run when both hand contacts AND both foot contacts are activated. So you have to link 4 signals, for which an AND gate with 4 inputs is necessary (AND 4 ).

realization

AND gates are produced as an integrated circuit (IC) by many manufacturers. Standard modules of this type are z. B. available under the designation "7408" in TTL technology and as "74HC08" in CMOS technology and contain four AND gates with two inputs each. The exact component name depends on the manufacturer. Logic gates of this type are available from electronics retailers for a few cents.

CMOS

The picture on the right shows the circuit diagram of an AND gate in CMOS technology. If there is high potential at inputs A and B, then T3 and T4 conduct, with T1 and T2 blocking. This means that T5 and T6 have low potential and T5 conducts and T6 blocks, which is why output Y has high potential. In all other input states, there is low potential at the output because T6 is conducting.

literature

- Ulrich Tietze, Christoph Schenk: Semiconductor circuit technology . 12th edition. Springer, 2002, ISBN 3-540-42849-6 .