MME U80701

The U80701 is a replica of the microprocessor type MicroVAX 78032 of Digital Equipment Corporation (DEC), the means of reverse engineering was developed. It was the first 32-bit processor manufactured in the German Democratic Republic (GDR) and was developed to make the leading computer line of the Digital Equipment Corporation, especially the MicroVAX II, available in the GDR. The processor, which is part of the U80700 circuit system, was officially introduced on August 14, 1989. On October 6, 1989, the development collective for the circuit system was awarded the GDR national prize, 1st class, for science and technology.

The microprocessor should be used in the Robotron workstation computer K 1820 , a replica of the MicroVAX II. Ten samples were built from this system. At the Leipzig spring fair in 1990 the microprocessor was exhibited in a showcase of the VEB Mikroelektronik “Karl-Marx” Erfurt . The Soviet Union was interested in the circuit as well as in the K 1820. The U80701 processor was no longer manufactured in series. From 1995, a U80900 microprocessor system based on the CVAX 78034 model for the successor model K 1830 (corresponding to MicroVAX III) should replace the U80700 system.

architecture

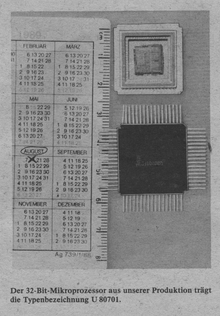

The CPU was housed in a 68-pin FlatPack- Plast or ceramic housing . The integrated memory management unit ( MMU ) could address up to 16 MB physical and up to 4 gigabytes of virtual memory and supported a 512 byte page-oriented protection mechanism as well as management of access rights.

Programming was carried out using 175 machine commands , 16 32-bit general registers and 20 processor or internal registers . The CPU had a 62.4 KB ROM with an integrated 8-byte prefetch stack . The ROM contained a program for flow control. The address and data bus occupied the same pins, which is why the multiplex method was used here. It was also possible to expand the CPU with an additional floating point unit .

The U80700 processor system included the following circuits:

- U80701: main processor (CPU)

- U80702: Reed-Solomon generator (RSG)

- U80703: Floating point processor (FPU)

- U80707: DIGITAL Link asynchronous receiver / transmitter (DLART)

- U80709: CPU interface gate array (CIGA)

- U80711: Bus Interface Gate Array (BIGA)

The individual components of the U80700 circuit system were developed under the direction of the Microelectronics Combine in Erfurt in collaboration with the Robotron and Carl-Zeiss Jena ( Microelectronics Center Dresden ) and the Central Institute for Cybernetics and Information Processes Berlin of the Academy of Sciences of the GDR . For example, Robotron-Elektronik Dresden (departments E9 and E5) was commissioned with the development of the U80702, U80703 and U80707 right through to samples according to the specifications.

Data

| Manufacturer: | VEB Microelectronics "Karl Marx" Erfurt |

| Designation: | U 80701 FC |

| Address bus: | 32 bit internal / external |

| Data bus: | 32 bit internal / external |

| Start of development: | 1986 |

| not working patterns: | 1988 |

| first working samples: | 1989 |

| Technology: | nSG ( NMOS - silicon gate technology ) |

| Number of transistors: | around 130,000 |

| Chip area: | 85 mm² |

| Clock frequency: | effective 5 MHz (derived from 40 MHz) |

| Processing speed K 1820 : | 0.9 MIPS |

| MMU : | integrated |

| Casing: | PLCC-68 according to source # 3, also known as CQFP-68 (see photos) |

| designation | An exit | description |

|---|---|---|

| CLK1 | entrance | Input clock |

| CLK0 | output | Clock output of the normal frequency |

| RESET # | entrance | RESET of the CPU |

| BM0..BM3 | Outputs | Byte mask |

| DAL0..DAL31 | Inputs / outputs | multiplexed data / address bus |

| AS # | Exit, tristate | Address strobe |

| DS # | Exit, tristate | Data strobe |

| DBE # | Exit, tristate | Data buffer enable |

| WR # | Exit, tristate | Write |

| EPS # | output | External processor strobe |

| CS0, CS1 | Outputs, tristates | Bus cycle status |

| CS2 | Input / output, tristate | Bus cycle status |

| RDY # | entrance | Ready |

| ERR # | entrance | Error |

| DMR # | entrance | DMA request |

| DMG # | output | DMA grant |

| STOP# | entrance | Halt interrupt request |

| INTTIM # | entrance | Timer interrupt request |

| PWRFL # | entrance | Power fail interrupt request |

| IRQ0 # .. IRQ3 # | Entrances | Interrupt request for standard I / O interrupts |

| TEST | entrance | Test input for component manufacturers |

| U CCX | - | Operating voltage to supply the pin logic of the data / address bus |

| U SSX | - | Reference potential for U CCX |

| U CCI | - | Operating voltage for circuit logic |

| U SSI | - | Reference potential for U CCI |

| U BB | - | Bulk voltage, generated internally |

swell

- Radio amateur. 38, H. 10, 1989, p. 473 (image # 2).

- Klaus Krakat: DDR-Kombinat develops its first 32-bit CPU. Computerwoche No. 41, October 6, 1989.

- Application center electronics: microelectronics complete overview. (PDF; 1.1 MB) Info-Verlag electronic, Berlin 1990, pp. 234-236.

- Collective of authors: Technical manual ZVE KAC20. VEB Robotron-Elektronik Dresden, December 1989.

Web links

- Picture of prototypes U80701 and U80703 Picture by Ulrich Zander

- Comparison of chip photos from the DEC 78032 and U80701

- Soviet, microVAX II-compatible mainboard M10 with U80701FC

- DEC's first single chip VAX microprocessor 78032 (DC333) at The Computer History Simulation Project

- Könau, St .: Celebration for the wrong chip. Mitteldeutsche Zeitung, January 8, 2010, article on the handover of the U80701 to Erich Honecker

- Pictures from the Federal Archives for the handover of the U80701 to Erich Honecker

Individual evidence

- ↑ Specifications workstation 32 bit K 1820 based on the MP 700 microprocessor family. VVS d 063-247 / 89, VEB Robotron-Elektronik Dresden, March 1989, Saxon State Archives Dresden 11594-1361 / 1-2 (PDF file 4.8 MB).

- ^ Dieter Walter: History of the VEB Robotron Electronics Dresden. Dresden 2006, pp. 40-41. (PDF file; 1.1 MB)

- ^ WE Schlegel: Fair report LFM 1990 . In: radio television electronics . No. 6 , 1990, ISSN 1436-1574 , pp. 345 .

- ↑ Author collective: Concept for the development of computing technology up to the year 2000. 1st version. VVS d 063-430 / 89, VEB Kombinat Robotron, Dresden, September 15, 1989 (PDF file 11.7 MB)

- ↑ Electronics application center: complete overview of microelectronics. (PDF; 1.1 MB) Info-Verlag electronic, Berlin 1990, p. 236.

- ↑ requirement specifications U80702 , U80703 , U80707. VVS d 063–284 / 89, VVS d 063–267 / 89, VVS d 063–270 / 89, VEB Robotron-Elektronik Dresden, February 1989, Saxon State Archives Dresden 11594-1361 / 1-2