Shift register

A shift register is a logic switching mechanism . Several flip-flops connected in series move their memory content (1 bit each) one flip-flop further with each work cycle - visually similar to a chain of buckets . The number of memory locations in the register is constant.

Shift registers work according to the FIFO principle. The bit saved first leaves the memory first. Shifting in and out, reading in and reading out are done synchronously , a shift register can only be used as a queue to a limited extent .

Shift registers are often expanded with additional logic (consisting of several logic gates ). This can ensure

- that the highest bit is shifted into the lowest bit (there is a rotation, one also speaks of a circular shift register ),

- that it can be operated bidirectionally, i.e. the direction of the shift is variable,

- that it can be determined whether the released bit should be set or deleted, and / or

- that the register can be written to or read out in parallel.

construction

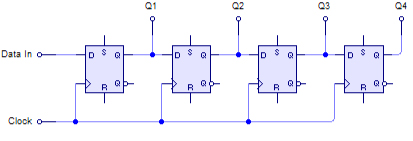

.

The 4-bit shift register shown in this figure is essentially based on the actual shift register consisting of the flip-flops D00, D10, D20 and D30. The connections are defined as follows:

- A value can be read in parallel via the connections d0 to d3.

- The value stored in the shift register can be read out in parallel via the connections Q0 to Q3.

- A value can be read in serially via the data-in connection (DI) and read out serially via the data-out connection (DO).

- The connections Clock (CLK), Load (LD) and Enable (EN) are used for control.

Data in and data out

The data-in and data-out connections can fulfill different functions depending on the wiring:

- Serial reading at the data-in connection and serial output of data at the data-out connection.

- Construction of a ring register by connecting the data-out and the data-in connection.

- Serial expansion of the shift register by additional shift registers to process larger word widths. For this purpose, the data-out connection is connected to the data-in connection of the subsequent shift register.

Clock

With a positive edge at the clock input, the bit stored in the respective flip-flops is output at the output, thus passed on to the following input gate (D00 → D11; D10 → D21; etc.) and held until another positive edge occurs at the clock input.

Load

If the load input is set to high, the bits of the upstream flip-flops (or the DI input) applied to the input gates (D01, D11, D21 and D31) are read. If, on the other hand, the load input is low, the bit of the upstream flip-flop (or DI input) is ignored and the bit at the associated parallel input is read in instead. The bit that has been read is passed on to the subsequent flip-flop (or DO output).

If parallel reading is not required, gates D01, D11, D21 and D31, as well as inputs d0 to d3 can be omitted and the outputs of the flip-flops (or data-out) can be directly connected to the inputs of the subsequent flip-flops (or data-in) are connected.

Enable

The enable input controls the output buffer consisting of gates D02, D12, D22 and D32. In the event of a positive edge, the bit pattern stored in the shift register is taken over from the output buffer and output at the parallel output with the connections Q0 to Q3. The value is held until there is another positive edge at the enable input.

If no output buffer is required, the enable input and gates D02, D12, D22 and D32 can be omitted. In this case, the outputs Q0 to Q3 are connected directly to the output of the associated shift register flip-flops.

Structure of a bidirectional shift register

To implement a bidirectional shift register, either two shift registers are required, or tristate gates that can dynamically switch the internal connections of the register.

When implemented with the aid of two shift registers, the parallel input of one register is crossed with the parallel input of the other register and vice versa. This means that the value can be copied from the register shifting to the left into the register shifting to the right and vice versa.

use

Serialization and parallelization of bit patterns

Shift registers are part of converters between serial and parallel data. A serialization or parallelization of bit patterns can be implemented using shift registers. In the case of serialization, it must be possible to load the respective bit pattern into the shift register in parallel; H. every flip-flop needs a load input. Otherwise there would already be a serial representation. With parallelization, each flip-flop must have a readable output so that the values of the entire shift register can be read out in parallel at a certain point in time. The SPI interface used by most µ-controllers is a shift register-based bus system with which SR logic modules can be used directly as parallel outputs (ports).

Bit shifting in machine languages

Most machine languages have a shift command on the registers. This means that you can often even multiply faster in machine language by shifting and adding than with the generic multiplication command / multiplication algorithm. For example, you can multiply by 320 more quickly by first copying the register, then shifting one register by 8 bits (multiplication by 256) and shifting the other register by 6 bits (multiplication by 64) and then adding the two registers. Furthermore, when the bit is shifted, the bit that has dropped out is not omitted, but is usually stored in a flag in the flag register and can then be processed further. A distinction is made between logical and arithmetic sliding. With arithmetic shifting, positive numbers remain positive and negative numbers remain negative. The most significant bit is not changed for this purpose.

Multiplication of binary numbers

The multiplication of two binary numbers is done by shifting and adding (e.g. by the Booth algorithm ). In microprocessors this is achieved through shift registers. A data signal is thus shifted further. Is z. For example, if the signal state is "high", this is shifted to the next bit.

Use as a buffer

To filter digitized signals, a signal processor buffers a fixed number of values. This can be done in shift registers.

Generation of pseudo random numbers

To generate pseudo-random numbers can linear feedback shift registers are used.

Cyclical redundancy check

The cyclic redundancy check ( English cyclic redundancy check, CRC ) with a can by exclusive-OR gates are implemented in hardware feedback shift register.

building blocks

The following table lists some commercially available shift registers as examples:

| Word length | Logic family | description | ||

|---|---|---|---|---|

| TTL | ECL | CMOS | ||

| 4 bit | 74LS194A | 10141 | 40194 | in / out serial / parallel |

| 8 bit | 74LS164 74LS299 |

74HC595 4014 |

serial in parallel out parallel in serial out |

|

| 16 bit | 74LS673 | 4006 | ||

| 8 × 1… 16 bit | Am29525 | |||

See also

literature

- Ulrich Tietze, Christoph Schenk: Semiconductor circuit technology . 12th edition. Springer, Heidelberg 2002, ISBN 3-540-42849-6 .