Synchronous counter

A synchronous counter is an electrical component in digital technology that counts a sequence of events. Each resulting number is saved until the next event. In the simplest case, the counter reading is represented in numbers of the dual system . In this case, the possible numbers are limited to the number of binary storage elements present . One then speaks of n-bit synchronous counters . With suitable switching, counters in the decimal system are also possible and widely used. The input signal to be counted is also referred to as a clock signal in the case of a periodic sequence .

Synchronous counters belong to the synchronous circuits because all memory elements can only change on a fixed (rising or falling) edge of a common signal. This simultaneity of all storage elements is necessary if the counter reading is to be taken over by an electronic device (e.g. microprocessor) shortly after the event (e.g. after ½ period ).

construction

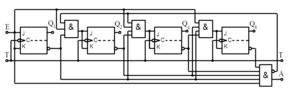

A synchronous counter can be constructed from JK flip-flops , for example in the diagram opposite. The trigger input of each flip-flop is connected to the signal of the event to be counted via the input CLK. This structure allows all flip-flops to run synchronously with each other and gives the circuit its name (in contrast to the asynchronous counter ).

By connecting the inputs of each individual flip-flop, their output signals can be understood as a sequence of digits. In the example, each output represents the digit of a four-digit binary number, with Q 0 in the least significant place. With other circuits, for example, four flip-flops can be used to represent the 8-4-2-1 code of a decimal digit, see frequency divider .

A JK flip-flop behaves like a T flip-flop when both inputs have the same level . With J = K = 1 the level at the output changes and with J = K = 0 it remains unchanged. This property is used for the synchronous counter. In the following, a 4-bit up counter with the outputs Q 0 to Q 3 is described, which counts the numbers from to in natural order.

|

|

|

This results in the following interconnection:

- Bit Q 0 with the lowest priority (2 0 = 1) should change with every rising signal edge and is therefore connected directly to the clock input CLK.

- The bit Q 1 with the next highest priority (2 1 = 2) should only change if the output Q 0 has level 1 (i.e. it output a 1 during the previous cycle). This is realized by connecting the output to the J and K inputs of the second flip-flop.

- The next bit Q 2 with the next higher value (2 2 = 4) should only change if all lower value bits (Q 0 and Q 1 ) have the level 1 (i.e. the binary number 11 was displayed during the previous cycle). This is determined with an AND gate .

- The last bit Q 3 with the highest value (2 3 = 8) should only change if all lower value bits (Q 0 , Q 1 and Q 2 ) have level 1 (i.e. the binary number 111 represented in the previous cycle). This can be done with an additional AND gate, which uses the result from the previous step.

The example can be continued in this way to generate counters of any size . If, as in the explanation of the last step, previous results are used, the counting speed is severely limited. In order to achieve a correct state change of the most significant bit, the information about the state change of the least significant bit must have migrated from the last clock edge through the entire chain of AND gates at the time of the corresponding clock edge. For example, the gate delay times of the 74HCxx series of logic modules of typically 15 ns ensure that a synchronous counter of the type described, which counts at only 10 MHz, cannot even be 8 bits long! - The chain connection can be avoided by using AND gates with several inputs.

properties

In the type described in the last section, gate delay times (switching time-related delays) add up. This can be avoided in that each stage generates its input signal with its own AND gate, which combines all less significant bits. For example, the JK flip-flop of bit 7 requires an upstream AND gate that detects bits Q 0 to Q 6 on seven inputs . In such a construction, the synchronous counter has the advantage over the asynchronous counter that gate delay times do not add up and thus higher clock rates or larger counters are possible with the same clock rate. The price is a significantly higher level of complexity, which, however, can be easily implemented in FPGA or dedicated integrated ICs.

variants

Down counter

A synchronous binary down counter formed by the in the above-shown circuit instead of the Q outputs Q outputs are used. The down counter counts down one step with each cycle. When the lower limit value 0 is reached, the down counter jumps back to the maximum value in the next step.

A synchronous countdown in decimal numbers is also possible. The circuit shown for a decimal digit can be cascaded as required. The BCD code is picked up at the normal Q outputs. To enable the counter, input E is connected to logic 1; in the subsequent circuits, E is connected to A of the preliminary stage. The signal to be counted is applied to T and connected through all stages. After the output signal 0000 2 = 0 10 , the next falling edge at T leads to the value 1001 2 = 9 10 , and a carry count step is carried out.

With D flip-flop

The adjacent circuit shows an up counter with D flip-flops . As soon as all lower-valued flip-flops have switched to 1 (detection by the AND gate), the input of the next flip-flop is inverted (by feedback of its own state and an XOR link with the result of the AND gate). This scheme can also be continued as required without affecting the maximum counting speed in order to implement larger counters.

To turn the logic circuit shown into a down counter , the inverse flip-flop outputs ( Q x ) are used for the counter reading. The remaining combinational logic for controlling the respective subsequent flip-flops remains unchanged. With this counter, too, Q 0 is the least significant bit (LSB).

Reversible counter

For example , when measuring positions by means of incremental encoders , if both directions of movement are permissible, counters are required that can count up and down. A direction detection must supply an additional control signal to the counter. Circuits for this are described in the literature. These counters are always synchronous counters.

Individual evidence

- ↑ F. Dokter and J. Steinhauer: Digital electronics in measurement technology and data processing, Volume II: Application of digital basic circuits and device technology. Philips reference books, 3rd edition 1973, pp. 55 ff

![\ left [0; \, 2 ^ n-1 \ right]](https://wikimedia.org/api/rest_v1/media/math/render/svg/c978f17b649c474fe582a122171def918cdc4248)