Emitter-coupled logic

An emitter coupled logic ( English emitter coupled logic , ECL) denotes electrical circuits for logic gates in the digital technology . As in the transistor-transistor logic , the bipolar transistor is used as the active component in these circuits . However, the ECL technique is much faster; i.e., it has shorter gate delays. The high power dissipation and the need for a positive and negative supply voltage are disadvantageous. Positive emitter-coupled logic (PECL) is an extension with lower power loss and which only needs a positive supply voltage . A low-power version of the PECL with a low supply voltage in the range below 3.3 V is LVPECL ( Low Voltage Positive Emitter Coupled Logic ).

construction

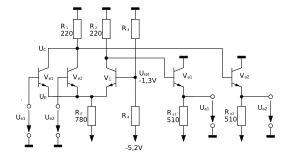

ECL gates are usually operated with a negative operating voltage. The basic element of an ECL circuit is a differential amplifier . Several transistors are connected to one another via the emitter connection and are routed together via a constant current source . In the figure, the differential amplifier of the input transistors is V e1 and V e2 and transistor V 1 formed. The number of transistors for the inputs depends on the circuit and can be expanded if necessary. A constant voltage ( U ref ) is applied to the base of V 1 via a voltage divider consisting of resistors R 3 and R 4 . When the input voltages U e1 and U e2 have a low level, the transistors V e1 and V e2 block . As a result, the emitter current flows through the transistor V 1 and thus causes a voltage drop across the resistor R 2 , whereby the transistor V a1 is activated. As a result, U a1 goes to the low level and U a2 to the high level. Thus, in positive logic, the output with U a1 is the output of an OR link and the output with U a2 is the output of a NOR link .

The gain per differential stage is in the normal range of 30 times for digital circuits and is limited by the level of the operating voltage. This can lead to parasitic oscillations with slow input edges, since the logic always remains in the linear range. However, high-frequency amplifiers, oscillators (> 1 GHz), line receivers and comparator circuits with extreme data rates are also possible.

The ECL family is one of the fastest logic families available. This is achieved because (unlike, for example, transistor-transistor logic ) no transistor saturates in the normal operating state. With ECL circuits, delay times of <200 ps can be achieved, which means that ECL circuits are faster than Schottky TTL circuits , which also do not go into saturation. The reason for the difference is that the collector-emitter voltage on the conducting transistors is higher at> 0.6 V, which not only results in a greater distance to saturation, but also a reduction in the collector-base junction capacitance . A further increase in speed results from the small signal amplitudes when switching over of only 0.8 V. This means that the junction capacitances are quickly reloaded. The low output resistance r a of the emitter followers also accelerates the speed. The output resistance results from the relationship between the collector circuit :

In addition, an almost constant current flows through the circuit. There are no strong current peaks as with other logic families.

Compared to other logic circuits, the power consumption is very high when the gate does not switch. However, CMOS has the advantage that it can be integrated cheaply and the ongoing miniaturization can be implemented more easily.

Dimensioning

In the event that the transistor V 1 blocks, a voltage drop of approximately 0.2 V occurs across the resistor R 2 , which is caused by the current at the base via the transistor V a1 . For the voltage U a2 at the emitter of the transistor V a2 , the equations of the differential amplifier result in an electrical potential of approximately −0.9 V, which represents the high level. If this high level is applied to one of the inputs, the following results for the electrical potential U E :

To prevent the transistors at the input from saturating, the collector-emitter voltage should not drop below 0.6 V. From this follows the minimum collector potential:

Therefore the low level is chosen to be −1.7 V. The reference voltage U ref must now be selected in such a way that the input transistors become conductive with a high input voltage of −0.9 V and block with a low input voltage of −1.7 V. This is achieved by setting U ref to a value exactly between these values:

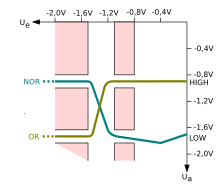

With the highest permissible input low level of U Low, max = −1.5 V, a high level of at least U a2 = −1.0 V must be present at the NOR output . At the lowest permissible input high level of U High, min = −1.1 V, the low level at the output may have a maximum of −1.6 V.

In contrast to the other logic families , the input voltage in the high access is very limited and must not exceed −0.8 V so that the input transistor does not come into saturation. This is noticeable in the transfer characteristic as a kink at around −0.4 V at the NOR output. If the voltage at the input increases further, the potential at its collector and emitter ( U C and U E ) falls due to the saturation of the input transistor , as a result of which the voltage U a2 at the output increases.

The characteristic curve shows that the logic levels are closer to zero potential than to the negative operating voltage. In addition, the size of the operating voltage is no longer relevant for the logic level, since it is only determined by the base-emitter voltage of the emitter follower . If one were to define the negative level as the reference potential, it would superimpose the levels, which would not allow reliable operation due to the low level.

The power loss of a single gate type MC10xxx is 25 m W . In addition, there is a power loss at the emitter resistors, which amounts to another 30 mW each with an average output voltage of −1.3 V and 510 Ω. This is more than the entire gate is consumed. Emitter resistors are therefore only connected when gates are used, which is why they are not accommodated in the IC housing. The power loss at the emitter resistors can be reduced to around 10 mW if the operating voltage is reduced to −2 V and the resistances are only 50 Ω. However, the voltage in the power supply must be generated efficiently (i.e. with a high degree of efficiency ), otherwise the power dissipation will only be shifted from the circuit to the supply. The −2 V are therefore not generated from the −5.2 V with a series regulator . However, the additional effort required for the supply only makes sense with many ECL gates.

Wired-OR

By connecting ECL outputs in parallel , a logical OR operation can be achieved due to the open emitter outputs , comparable to wired AND with open collector outputs on a TTL circuit . The advantage of this link is that you save power loss and latency in addition to or due to the saving of the gate.

The diagram on the right shows the structure of the circuit. The connection is made by wiring the OR and NOR outputs:

application

Due to their high power consumption, ECL gates are not suitable for VLSI circuits, i.e. extremely high integration. However, they are specifically used where extremely short switching times and / or constant power consumption with frequent gate changes are important, for example in a particularly fast ALU of a microprocessor . However, in some areas, the ECL technology is increasingly being replaced by the continuously improving CMOS technology.

Another area of application for ECL technology are bus drivers for extremely fast differential signal transmission (see symmetrical signal transmission and LVDS ).

See also

- Diode-transistor logic (DTL)

- Resistor-Transistor Logic (RTL)

- Slow Fail-Safe Logic (LSL)

Individual evidence

- ↑ Introduction to LVDS, PECL, and CML (HFAN-1.0). (PDF) Maxim Integrated Circuits, April 2008, accessed April 30, 2014 .