SPARC architecture

The SPARC architecture ( S calable P rocessor ARC hitecture ) is a microprocessor architecture that is mainly used in Oracle products . There are also other manufacturers, such as Fujitsu Technology Solutions (formerly Fujitsu Siemens Computers).

history

Sun Microsystems developed from 1985 and marketed the first generations of SPARC processors from 1987. In 1989 the not-for-profit organization SPARC International was founded as a point of contact for the further development of the open SPARC architecture.

At the time of development, Sun was already the second largest manufacturer of workstations with the Unix operating system (market share 1985: Apollo Computer 41%, Sun 21%). With the SPARC processor, the company, like many workstation manufacturers at the time, wanted to create a RISC processor architecture that would replace the 68020 and i386 roadrunner processors and would remain competitive for many years. The processors were made by other manufacturers such as Texas Instruments or Fujitsu .

Sun brought out many workstations and servers with its Sun 4 series that used the SPARC processor. But Fujitsu also built SPARC processors into its PrimePower systems up until 2005. In addition to SunOS or Solaris , Linux or the modern BSD variants can also be used on SPARC systems . In 1995 the original 32-bit architecture was expanded to 64-bit and marketed under the name UltraSparc. In addition to additional units, this architecture has a deeper pipeline and some simple SIMD commands ( Visual Instruction Set (VIS) ). The Ultrasparc standard has four main versions so far, the current version is UltraSparc T2 .

The outstanding feature of the architecture is a register file , which originally consisted of 128 32-bit registers. The CPU can only access part of it, usually 32, directly. The CPU sees 24 of these in a window that can be moved using the software (→ register window ). This means that arguments and results of subroutines can be transferred without having to copy registers by moving the window.

The floating point unit can be used as a 32-way, 32-bit, single-precision register, 16-way, 64-bit, double-precision register, or an 8-way, 128-bit, quad-precision register.

The current versions are 32-bit V8 and 64-bit V9. The SPARC V8 is completely Big Endian . The SPARC V9 uses instructions in Big Endian format, but supports both byte orders for data values. This can be switched both at instruction level by using special commands and for entire memory areas by means of an MMU setting. The latter is used in particular when memory areas of devices have to be accessed, such as the PCI bus defined as Little Endian .

A simple version of a SPARC processor called LEON 1 in the hardware description language VHDL is freely available from ESA . Both the design of the UltraSPARC T1 and that of the UltraSPARC T2 were published in 2006 and 2007 under the open source license GPL via the OpenSPARC project and can be downloaded there. The design of the Sun Microsparc has also been published in source code since mid-1990 and is freely usable.

There are also a number of microcontroller implementations (for example from Hitachi ), some of which, however, have a compressed machine code and are therefore not binary compatible.

Since the takeover of Sun Microsystems by Oracle , SPARC has now belonged to Oracle.

Models

various implementations of the SPARC architecture, including Sun's successful SuperSPARC and UltraSPARC-I:

| Sun SPARC microprocessor specification | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| model | Frequency [MHz] |

Architecture version |

year | Process [µm] |

Transistors [millions] |

Core dimension [mm²] |

IO pins | Recording [W] |

Voltage [V] |

L1 Dcache [k] |

L1 Icache [k] |

L2 cache [k] |

L3 cache [k] |

| SPARC | 14.28-40 | V7 | 1987-1992 | 0.8-1.3 | ~ 0.1-1.8 | - | 160-256 | - | - | 0-128 | no | no | |

| microSPARC I | 50 | V8 | 1992 | 0.8 | 0.8 | 225 | 288 | 2.5 | 5 | 4th | 2 | no | no |

| SuperSPARC I | 33-65 | V8 | 1992 | 0.8 | 3.1 | 256 | 293 | 14.3 | 5 | 16 | 20th | 1024 | no |

| microSPARC II | 60-125 | V8 | 1992 | 0.5 | 2.3 | 233 | 321 | 5 | 3.3 | 8th | 16 | no | no |

| SuperSPARC II | 75-90 | V8 | 1994 | 0.8 | 3.1 | 299 | - | 16 | - | 16 | 20th | 2048 | no |

| TurboSPARC | 170-180 | V8 | 1995 | 0.35 | - | - | - | 7th | - | 16 | 16 | 1024 | no |

| UltraSPARC I | 140-200 | V9 | 1995 | 0.5 | 5.2 | 315 | 521 | 30th | 3.3 | 16 | 16 | 1024 | no |

| UltraSPARC II | 250-480 | V9 | 1997 | 0.25 | 5.4 | 156 | 521 | 21st | 3.3 | 16 | 16 | 8192 | no |

| UltraSPARC IIi | 270-650 | V9 | 1998 | 0.25 | 5.75 | 148 | 370 | 17.6 | 1.7 | 16 | 16 | 2048 | no |

| UltraSPARC IIe | 400-500 | V9 | 2000 | 0.18 | 5.4 | - | 370 | 13 | 1.7 | 16 | 16 | 256 | no |

| UltraSPARC III | 600-1200 | V9 | 2001 | 0.13 | 29 | 330 | 1368 | 53 | 1.6 | 64 | 32 | 8192 | no |

| UltraSPARC IIIi | 1064-1600 | V9 | 2003 | 0.13 | 87.5 | 206 | 959 | 52 | 1.3 | 64 | 32 | 1024 | no |

| UltraSPARC IV | 1050-1350 | V9 | 2004 | 0.13 | 66 | 356 | 1368 | 108 | 1.35 | 64 | 32 | 16384 | no |

| UltraSPARC IV + | 1500-2100 | V9 | 2005 | 0.09 | 295 | 336 | 1368 | 90 | 1.1 | 64 | 64 | 2048 | 32768 |

| UltraSPARC T1 | 1000-1400 | V9 | 2005 | 0.09 | 279 | 379 | 1934 | 79 | 1.3 | 8th | 16 | 3072 | no |

| UltraSPARC T2 | 900-1400 | V9 | 2007 | 0.065 | 503 | 342 | 1831 | 95 | 1.2 | 8th | 16 | 4096 | no |

| UltraSPARC T2 + | 1200-1600 | UA2007 | 2008 | 0.065 | 503 | 342 | 1831 | - | - | 8th | 16 | 4096 | no |

| UltraSPARC T3 | 1650 | UA2007 | 2010 | 0.04 | - | 371 | - | 139 | - | 8th | 16 | 6144 | no |

| UltraSPARC T4 | 2850-3000 | OSA2011 | 2011 | 0.04 | 855 | 403 | - | 240 | - | 16x8 | 16x8 | 128x8 | no |

| UltraSPARC T5 | 3600 | OSA2011 | 2013 | 0.028 | 1500 | 478 | - | - | - | 16x16 | 16x16 | 128x16 | 8192 |

| Ross / Bridgepoint SPARC microprocessor specification | |||||||||||||

| HyperSPARC A | 55-80 | V8 | 1993 | 0.5 | 1.5 | - | - | - | 5 | no | 8th | 256 | no |

| HyperSPARC B | 90-125 | V8 | 1995 | 0.4 | 1.5 | - | - | 25th | 5 | no | 8th | 256 | no |

| HyperSPARC C | 110-166 | V8 | 1995 | 0.35 | 1.5 | - | - | 45.5 | 5 | no | 8th | 1024 | no |

| HyperSPARC D | 180-200 | V8 | 1995 | 0.35 | 1.7 | - | - | - | 5 | 16 | 16 | 1024 | no |

| Sun / Fujitsu SPARC64 processors | |||||||||||||

| SPARC64 V | 1350-2160 | V9 | 2004 | 0.13 | 191 | 290 | 269 | 40 | 1.2 | 128 | 128 | 2048 | no |

| SPARC64 VI | 2150-2400 | V9 | 2007 | 0.09 | 540 | 422 | - | 120 | - | 128 | 128 | 6144 | no |

| SPARC64 VII | 2700 | V9 | 2008 | 0.065 | 600 | 445 | - | 135 | - | 64 | 64 | 6144 | no |

| SPARC64 VIII | 2000 | V9 | 2009 | 0.045 | 760 | 513 | - | 58 | - | 32 | 32 | 4096 | no |

| SPARC64 X | 3000 | V9 | 2013 | - | - | - | - | - | - | - | 32 | - | 24576 |

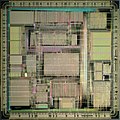

" The " of a TI microSPARC I

See also

Web links

- LEON2 and LEON3 SPARC VHDL models (under LGPL license)

- SPARC processors: Pictures and descriptions on cpu-collection.de

- OpenSPARC project page

- SPARC64 V Background Briefing (English)

- Multi-core multi-thread processor SPARC64 VI (English)

- MPF: Fujitsu presents new SPARC64 V-CPU

Individual evidence

- ↑ Jens Ihlenfeld: OpenSPARC T2: Sun puts UltraSPARC T2 under the GPL. In: Golem.de . December 12, 2007, accessed April 2, 2017 .

- ↑ http://www.opensparc.net/ . Sun Microsystems. Retrieved July 12, 2009.

- ↑ Fujitsu launches 'Athena' Sparc64-X servers in Japan . the register. Retrieved February 27, 2013.