Frequency divider

A frequency divider is an electronic circuit that reduces an input frequency in a certain integer division ratio. The circuits for this are implemented largely digitally , for example with counting circuits made up of bistable multivibrators or with ring counters .

The input signal is a square wave voltage , one edge of which is evaluated. This must be steep enough; their rise or fall time must not exceed certain values, which are of the order of 50 ns for the TTL components that are preferably used . Other signal curves (for example sine) must be converted into a square wave using a Schmitt trigger . The Schmitt trigger is partly already included in integrated flip-flops. The output waveform can be symmetrical or asymmetrical.

functionality

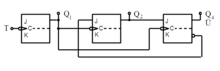

To enable the counter, input E is connected to "logical 1"; If there are counting levels attached for more significant digits, E is connected to output A of the preliminary stage. The signal to be counted is applied to T and connected through all stages.

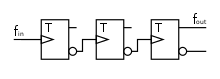

To set up simple asynchronous frequency dividers for square signals, edge - controlled flip - flops can be connected directly one after the other. Some flip-flop designs change their output signal to the opposite on a fixed (rising or falling) edge in the input signal with suitable switching. After every two of these edges at the input, a rectified edge occurs at the output, see “Q 1 ” versus “T” in the signal-time diagram ; the frequency of an applied clock is divided by 2.

For use as a frequency divider, there are special flip-flop circuits, which are also known as counters . The division ratio is preferably the powers of 2 or 10. Other divisions are also possible through suitable wiring. The circuit diagram of the divider 10: 1 contains a divider 2: 1 and a divider 5: 1. The divisor 6: 1 is made up of divisors 2: 1 and 3: 1. Similar circuits can be connected in series, for example for a ratio of 1000: 1. A reset line that can bring each memory element into a defined initial state independently of the clock cycle is not shown, but is always required.

A distinction is made between asynchronous counters , in which delays occur due to gate delay times , and synchronous counters , which are faster and often more complex. Another possibility are so-called machines .

In addition to electronic methods for frequency division, mechanical, pneumatic and optical principles can also be used.

application

Digital-electronic frequency dividers are widely used. They can be found, for example, in quartz watches , computers and their clock generators , in the PLLs of radio and television sets , electronic organs , stepper motors and measuring devices such as frequency counters , timers and voltmeters based on the dual slope method . If the frequency is known, for example from a quartz oscillator , frequency dividers become timers in which a period of time is generated proportional to the division ratio of period durations.

Measurement limits

Standard circuits reach around 100 MHz (10 8 Hz), the fastest circuits can work up to around 10 11 Hz. The combination of very fast electronics and laser is called a frequency comb and allows measurements up to 10 15 Hz.

Individual evidence

- ^ Dieter Stoll: Circuits of communications engineering. Vieweg, 1988, p. 139