Motorola 68000

The Motorola 68000 is a 1979 introduced CISC - processor from the 68000 family from Motorola (later Freescale , now NXP ). It has internal 32-bit registers , a linear address space addressed with 32 bits , 24 of which are externally available, eight 32-bit data registers, nine 32-bit address registers, a 16-bit status register and a 16-bit data bus .

One variant is the Motorola 68008 , in which the data bus is reduced to 8 bits and the address bus to 20 bits in the DIP version (or 22 bits in the PLCC version). The Motorola 68010 came onto the market as an improved version, which has been corrected for errors and offers improved support for virtual memory . A 68010 with an extended address bus of 31 bits was offered as the Motorola 68012 . The 68020 , 68030 , 68040 and 68060 followed later .

According to a modern legend , the designation 68000 comes from the number of transistors the processor has. In fact, it is the logical continuation of the type designation of the older 8-bit Motorola processor family Motorola 6800 . The architecture of the 68000 family is based on mainframes such as: B. IBM360 and the LSI11 / PDP11 from Digital Equipment, but with a linear address range that can be accessed directly without procedures such as multiplexing, segmentation or paging .

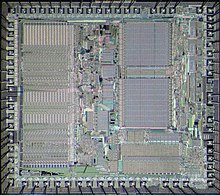

The 68000er (also called 68k) with 8 MHz clock frequency came on the market in a 64-pin DIL housing (see picture).

Architecture and instruction set

The processors of the 68000 family are characterized by the large number of registers and a largely orthogonal instruction set , i. H. almost all machine commands can be used with all types of addressing. The command set is structured as follows:

- COMMAND.s <ea1>, <ea2>

The processors of the 68000 family are so-called two-address machines, whereby a variable data width with .s = {B, W, L} can be used for most commands (corresponds to 8, 16 or 32 bits) and for the two sources - and target operands <ea1> or <ea2> one of the 68000 addressing types can be used:

| Notation | description | example |

|---|---|---|

| Dn | Data register directly | CLR.B D0 |

| On | Address register directly | MOVEA.W A0, A1 |

| (On) | Address register indirect | CLR.B (A0) |

| (An) + | Address register indirectly with post increment | CLR.B (A0) + |

| - (To) | Address register indirect with predecrement | CLR.B - (A0) |

| d16 (An) | Address register indirect with 16 bit offset | CLR.B 255 (A0) |

| d8 (An, Ri.s) | Address reg. ind. with 8 bit offset and index register | CLR.B $ 44 (A0, D0.L) |

| d16 (PC) | PC-relative with 16 bit offset | CLR.B 22 (PC) |

| d8 (PC, right side) | PC relative with 8 bit offset and index reg. | CLR.B 10 (PC, A1.W) |

| #xxxxxxxx | Constant (Immediate) | MOVEQ.L # 15, D0 |

| $ xxxx | Direct memory with 16-bit address (absolute short) | CLR.B $ 8000 |

| $ xxxxxxxx | Direct memory with 32-bit address (absolute long) | CLR.B $ 1,1008,000 |

or the complex MC68020 / 30/40/60 addressing types:

| Notation | description | example |

|---|---|---|

| (dis1, An, Ri.s * scl) | Address reg. indirect with 16- / 32-bit offset | MOVE.B ($ 12345678, A1, A2.L * 2), D0 |

| ([dis1, An], Ri.s * scl, dis2) | Double indirect with Post-Index | MOVE.W ([5, A2], D0.W, $ 23456), D1 |

| ([dis1, An, Ri.s * scl], dis2) | Double indirect with pre-index | MOVE.W ([5, A2, D0.W], $ 23456), D1 |

| (dis1, PC, Ri.s * scl) | PC-indirect with 16- or 32-bit offset | JSR (CONTINUE, PC) |

| ([dis1, PC], Ri.s * scl, dis2) | PC-relative, double ind m. Post index | JSR ([JUMP, PC], D1,2) |

| ([dis1, PC, Ri.s * scl], dis2) | PC-relative, double ind. m. Pre-index | MOVE.L ([PARAMETER, PC, D1.W], 4), D1 |

The 68000 only has a 16-bit ALU and a 16-bit instruction set, which can handle 8, 16 and 32-bit data types (32-bit architecture). The types MC68020 / 030/040/060, on the other hand, have a 32-bit ALU.

Example of a typical M68000 command:

| JSR <ea> (Jump to subroutine) |

| Command format 0100 1110 10mm mrrr |

The command ( opcode ) is 16 bits wide. Three bits (m) are used for the addressing mode, three more bits for the register (r) used or an offset address ( displacement ).

0100 1110 1011 1010 becomes JSR (d16, PC) . Since the PC-relative addressing with offset address (displacement) is used here, the following word is used as a signed relative address (displacement). Other commands such as MOVEQ # n, Dx are even completely coded in 16 bits.

The ability of the 68000 to understand 32-bit wide addresses and data for almost all commands (which of course had to be read in several cycles on a 16-bit bus), simplified software development immensely, since it is a 32 Bit architecture acted.

In contrast to z. For example, on the Intel 8086 , it is easy to address data sets larger than 64 KiB . Because of the 16-bit ALU and the 16-bit data bus, the 68000 is often called a 16-bit processor, but it runs 32-bit software without complaint. Because of the 16-bit ALU z. B. a 32-bit addition twice the time. The circuit block for generating addresses, however, has a full 32 bits, so that e.g. For example, searching through text with 8-bit characters is no slower than would be expected from a pure 16- bit character . In addition, the text can be longer than 64 KiB without modification of the program. 68000 software is 32-bit software.

The 68000 ignores the content of the upper 8 bits of an address register when accessing the memory. This makes it possible to use these bits freely, for example for meta information on a pointer. This obviously leads to problems with later processor generations from the 68000 family with 32-bit external address bus. Since this type of programming was very common on the early Macintosh computers, later Macintosh versions with 68020 processors without a memory management unit (MMU) had a special component called the Address Management Unit (AMU) instead of the MMU, which was the Optionally masked out the upper 8 bits of addresses in order to be able to use old software in a 24-bit compatibility mode . As a processor with nanocode and microcode , the 68000 can to a certain extent be programmed by the manufacturer on the hardware level. This led to such interesting variations like the 68000-360, directly on the chip, a scaled-down version of the IBM - System 360 / could run -Befehlssatzes and was used for a small 360 model from IBM.

The longest command of the 68k is 22 bytes long and is a MOVE command which copies data from one memory location to another, where both memory locations are addressed twice-indirectly with 32 bit displacements.

variants

The first variant was the 68008, in which only the nanocode was changed so that the data bus was only addressed with a width of 8 bits. Another variant was the 68010, which could be operated much better with virtual memory and also had some detail improvements. An offshoot of the 68010 was the not long available 68012, which provided more address lines for larger memories (up to 2 GiB). Later, variants were mostly derived directly from the original CPU, such as B. the 68EC020 from the 68020 (24 instead of 32 address lines) - or the 68EC040 and the 68LC040 from the 68040 (either the FPU or the MMU were missing ). Starting with the 68020 , the first 64-bit commands were also integrated step by step (for simple multiplications).

Interrupts with seven different priorities can be triggered via three binary-coded interrupt lines , the highest of which cannot be masked. Together with the corresponding peripheral components, up to 256 vectorized interrupts are possible.

The processor also contains control lines which signal whether a program command or a date is to be fetched next. This allows the construction of computers with separate memory for programs and data; a Harvard architecture is not possible, however, since the separate buses required for this for programs and data are not available here.

register

The register programming model can be divided into user and supervisor registers according to the two modes that the 68000 family has. These user / supervisor modes together with the exceptions (exception handling) form a protective mechanism and protect the system from crashes. The mode is displayed in the S bit of the status register SR. In supervisor mode you can use all resources of the CPU, in user mode only certain resources. This also explains the use of the programming model:

- User register model: is used by the user programmer or by a compiler

- Supervisor register model: used by the system programmer (operating system)

In a real-time multi-task system, the operating system core usually runs in supervisor mode and the user tasks or programs in user mode. This isolates the core from the user tasks. This protection can, for example, be extended to the hardware by using an MMU, since the CPU also outputs the status of the S bit in the status register SR in terms of hardware.

use

Thanks to the optional MMU, the CPU found its way into the Unix world as early as the early 1980s . It was installed in large numbers in the workstations from Apollo Computer (Apollo), HP (HP 9000-300) and Sun ( Sun-1 ) or from Digital Equipment Corporation (Vax 100) and SGI .

Personal and home computers followed in the mid-1980s, the first being Lisa from Apple , which was soon replaced by the Macintosh (Mac). It was also installed in the Commodore Amiga , the Atari ST and Sinclair QL (68008).

At the end of the 1980s and beginning of the 1990s it was found in game consoles such as the Sega Mega Drive or the Neo Geo . The processor was also used in chess computers (e.g. in the Fidelity Mach IV as 68020 with 20 MHz and Mephisto Amsterdam as 68000 with 12 MHz).

It is still used today in pocket calculators from Texas Instruments such as the TI-89 (Titanium) , TI-92 (Plus) and Voyage 200 . In the Airbus A320 , he controls the Elevator Aileron Computer (ELAC), which is part of the flight control system.

The main area of application of the processor was and is control computer in industry, mostly with a real-time operating system such as OS-9 or pSOS , Nucleus or Linux68k , whereby the latter is not a real-time operating system in the strict sense. This use and the widespread use were not least possible thanks to the good interrupt architecture and in combination with the VMEbus . The processor was also found in large numbers in laser printers . It was also used on LAN cards (Schneider and Koch) and on SCSI controllers (DPD), but also in modems ( Zyxel ). The automotive industry - primarily (motor) control units - also preferred to use the MC683xx controller family until the PowerPC appeared.

The high-performance models of the 68000 family are the 68040 and 68060 (up to 66 or 75 MHz). Since Apple switched to PowerPC CPUs after the 68040 , the 68060 was only used in expansion cards for the Amiga and the Atari Falcon 030 (CT60) as well as for special applications (e.g. in VMEbus computers from Motorola, for example , and embedded systems as used in BMW models of the 1990s or high-performance chess computers ).

Meanwhile, the great-68000 has largely disappeared, but is still in voting machines the company Nedap used. Motorola manufactures a variety of microcontrollers that descended from the 68000. The Motorola Coldfire family (development based on 68k) is still very popular in the area of embedded systems and goes up to the V5 with 400 MHz; this variant is used in HP laser printers. The DragonBall offshoots were used in the entry-level models of Palm PDAs and are common in simple cell phones .

A prominent example of a Coldfire-based (Amiga-inspired) system was the Metabox 1000 SetTopBox, which however never came onto the market.

Other components

The processors 68020 , 68030 , 68040 and 68060 had already integrated functions that were only introduced considerably later in other processor architectures:

- internal Harvard architecture

- Branch caches / prediction

- Barrel shifter

- Pipelining / prefetch

- User / Supervisor Mode (also called Protected Mode or Kernel Mode )

Other major achievements relate to the embedded controller (single chip) of the M68000 family, the M683xx family. These include B. the MC68332, MC68360, MC68376. These types were groundbreaking with the following features:

- BDM (Background Debug Mode). This resulted in the industry standard JTAG debugger, as the BDM used the JTAG lines or shared the lines. Under the IEEE-ISTO 5001-2003 and under the name Nexus, this became the standard interface for embedded systems. Both the physical interface and the protocol correspond to the Motorola BDM.

- Dual core, where the second CPU was used as an intelligent peripheral controller, e.g. B. with the

MC68332 as TPU - Timer Processing Unit or with the

MC68360 as CPM - Communications Processor Module or QUICC (Quad Integrated Communication Controller). This controller allowed the processing of all possible serial protocols. It is the predecessor of the well-known Power QUICC of the Power Architecture family.

literature

- C. Vieillefond: Programming the 68000 , Sybex Verlag, 1986, ISBN 3-88745-060-4

- Werner Hilf, Anton Nausch: M68000 Family Part 1 Basics and Architecture , te-wi (1984), ISBN 3-921803-16-0

- Werner Hilf, Anton Nausch: M68000 Family Part 2 Application and Building Blocks , te-wi (1984), ISBN 3-921803-30-6

- Werner Hilf: M68000 basics Volume 1 , architecture, hardware, instruction set, MC68020 / 30/40, MC68332, Franzis, Munich 1994, ISBN 3-7723-6333-4

- Werner Hilf: M68000 Applications Volume 2 , user and system programming, coprocessors, interface technology, software on diskette, MC68020 / 30/40, MC68332, Franzis, Munich 1994, ISBN 3-7723-6303-2

- Werner Hilf: Microprocessors for 32-bit systems , architecture, hardware, instruction set, market & technology, ISBN 3-89090-922-1