Base 5

| Base 5 | |

|---|---|

|

|

| Specifications | |

| introduction | At CeBit 1994 |

| design type | SPGA - ZIF |

| contacts | 320 |

| Bus protocol | own, Intel never introduced a designation |

| Bus cycle | 50 MHz, 60 MHz, 66 MHz |

| Operating voltage | variable voltage from 3.1 to 3.6 V. |

| Processors |

Intel Pentium (75–120 MHz) Intel Pentium Overdrive (125–166 MHz) Intel Pentium MMX Overdrive (125–200 MHz) AMD K5 (PR75 – PR200) IDT WinChip (180–200 MHz) IDT WinChip-2 (200–240 MHz) IDT WinChip-2a (233 MHz) and compatible |

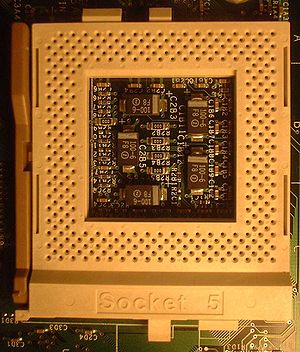

The base 5 is a processor socket and the successor of the base 4 . It is intended for early Pentium P54C processors. Later versions of the P54C and the successor P55C, on the other hand, use Socket 7 , which is largely compatible with Socket 5 in its original form and which could also accommodate all CPUs intended for Socket 5.

The bus protocol of Socket 5 is largely the same as that of Socket 4. The connections that have been added relate exclusively to the simplified dual processing , the Advanced Programmable Interrupt Controller ( APIC ) now integrated into the CPU and the power-saving modes of the new Pentium type. On the other hand, a few less important or rarely used connections of the first Pentium type P5 have been dropped. In addition, for reasons of power consumption, Intel has reduced the voltage supply for socket 5 to around 3.3 volts - depending on the CPU used. The logical signal levels have changed accordingly, but the signal timing still largely corresponds to that of the base 4.

A new pin, the BF pin, also allows the setting of different clock ratios between the processor bus and processor core in socket 5 . Many Socket 5 motherboards allow this pin to be set using a jumper called a BF or BF0 jumper. The first P54C Pentium (Pentium variants with 75 MHz, 90 MHz and 100 MHz) ran with a bus clock-to-core clock ratio of 2: 3, later (variants with 120 MHz or 133 MHz) with a ratio of 1: 2. With the BF0 jumper you could choose between these two ratios.

From the Pentium with 133 MHz onwards, socket 5 was replaced by socket 7 , which had practically the same function in its original form and instead of one BF pin had two, and later even three. Depending on the CPU used , it was possible to set up to four or eight different bus clock-to-core clock ratios.

It is incomprehensible that Intel initially made a distinction between Socket 5 and Socket 7. Functionally, there was initially a far smaller difference between the two than between the early and the late socket 7 type intended for the Pentium MMX .

The socket 5 is - like the socket 7 - a ZIF socket for staggered pin grid array layout (SPGA), i. H. the rows of contacts are staggered in order to achieve a higher packing density.