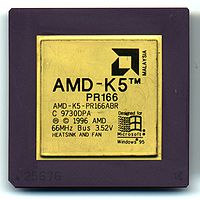

AMD K5

| << AMD K5 >> | |

|---|---|

|

|

| Production: | 1996 to 1997? |

| Producer: | AMD |

| Processor clock: | 75 MHz to 133 MHz |

| FSB cycle: | 50 MHz to 66 MHz |

| L1 cache size: | 24 kB |

| Instruction set : | x86 |

| Base: | |

Names of the processor cores:

|

|

The AMD K5 is an x86 - microprocessor , the first of AMD internally developed x86-compatible processor. It competed with the Intel Pentium , NexGen Nx586 and Cyrix 6x86 .

background

After AMD had only minimally modified Intel's microprocessor developments in the previous years, the manufacturer had to reorient itself after various legal disputes with Intel and seek its own development department and processor architecture. The K5 was the first result of this change in orientation, but this was associated with problems, as a result of which the K5 came to market much too late. The successor was the AMD K6 , which was not based on the K5, but on the NexGen Nx686 .

technology

Models

AMD struggled with development time and manufacturing yield, so the K5 hit the market a year later than originally planned. This version was still a kind of "pre-release", known as SSA / 5 , with errors in the L1 cache and in the branch prediction. It was first sold as the 5k86 and later also as the K5 . The bugfixed version, labeled 5k86 , was only sold as the K5 . The SSA / 5 series of the K5 included models from 75 to 100 MHz (5k86 P75 to P100, later K5 PR75 to PR100); 5k86 processors came on the market with clock frequencies from 90 MHz to 133 MHz (K5 PR120 to PR200).

architecture

The K5 is internally a RISC processor (based on the Am29000 RISC family) with an x86 decoding unit, which breaks down all x86 commands into RISC commands for execution. All modern x86 CPUs now work similarly.

The K5 has five integer units called out-of-order - pipelines are constructed and a non-pipelined FPU (the Intel Pentium has two designed as in-order pipeline integer units and a pipelined FPU). Register renaming and speculative execution improve the parallel execution options of the pipelines or reduce their blockage. The buffer for the branch prediction is four times larger than that of the Pentium (although the branch prediction itself does not work better) and the L1 cache is twice as large (and four times instead of twice associative). These improvements allow the K5 a higher integer performance than an equally clocked Pentium. For this reason, AMD used already by Am5x86 known P rating to indicate the performance relative to the Pentium. In the case of floating point calculations by the FPU, however, an AMD K5 works slower than a Pentium with a clock frequency corresponding to its P rating.

Model data

SSA / 5 (Model 0)

- Sales name: 5k86 P75 / P90 / P100; later K5 PR75 / PR90 / PR100

- L1 cache: 8 + 16 kB (data + instructions)

- Socket 5 and socket 7 with 50, 60 and 66 MHz front side bus

- Operating voltage (VCore): 3.52 V.

- Release DATE: March 27, 1996

- Manufacturing technology: 0.50 µm and 0.35 µm

- The size: 251 mm² (0.50 µm) and 161 mm² (0.35 µm) with 4.3 million transistors

- Clock rates (power consumption):

- 5k86 P75, K5 PR75: 75 MHz (11.63 W)

- 5k86 P90, K5 PR90: 90 MHz (13.96 W)

- 5k86 P100, K5 PR100: 100 MHz (15.51 W)

5k86 (Model 1)

- Sales name: K5 PR120 / PR133 / PR150 / PR166

- L1 cache: 8 + 16 kB (data + instructions)

- Socket 5 and socket 7 with 60 and 66 MHz front side bus

- Operating voltage (VCore): 3.52 V.

- Release DATE: October 7, 1996

- Manufacturing technology: 0.35 µm

- The size: 181 mm² (0.35 µm) with 4.3 million transistors

- Clock rates (power consumption):

- PR120: 90 MHz (12.37 W)

- PR133: 100 MHz (13.75 W)

- PR150: 105 MHz

- PR166: 116.6 MHz (16.04 W)

- PR200: 133 MHz (was originally planned, no longer sold)

See also

Web links

- AMD product page (English)

- Sandpile.org K5 information (English)

- Processor Charts ( Memento from April 23, 2009 in the Internet Archive ) (English)

- Processor Electrical Specifications ( Memento of May 3, 2009 in the Internet Archive )

- cpu-galerie.de Information and pictures about K5 processors

Data Sheets