Register (processor)

Registers in processors are memory areas for data that processors can access particularly quickly. You are in the immediate vicinity of the calculators . In a processor core , registers are at the top of the memory hierarchy and are therefore the fastest way to manipulate data, since access is independent of the data or address bus .

Many architectures , especially RISC architectures , only allow arithmetic units to process data in registers; other architectures also at least partially allow the use of non-register contents from the RAM or from hardware registers.

The register sets of different processor architectures differ in size, number and type of the available registers:

- Nowadays, individual registers are usually the size of a power of two, i.e. H. 8, 16, 32, 64, 128, 256 or 512 bit .

- The number of registers per core varies from five to several hundred.

- The different types of registers are described below.

Register types in a CPU core

According to characteristics

- Hardware register: physically available, "nameless", cf. physical memory address

- Architecture tab: are "visible" to the software, cf. logical memory address .

With old CPUs ( Z80 , Intel 486 ) the hardware and architecture registers are identical, with more modern CPUs (IBM System / 360 Model 91, Pentium Pro , AMD K5 , Intel Core ) it is different things.

According to the number of data values contained

- Scalar registers: contain a single data value, mostly integers , which can also be used as addresses .

- Vector registers: registers that contain several data values (usually 2 to 64) as a vector . The individual data values can each have a size of 8 bits to 64 bits and be integers or floating point numbers .

According to application function

Data register, accumulator

Data registers are used to store operands for the ALU and its results. With older processor architectures there was sometimes only one such register, the accumulator ; New generation processor cores often have several data registers with an accumulator function.

As a rule, the size of the data register together with the width of the data bus are decisive for classifying a processor architecture as an 8-, 16-, 32- or 64-bit architecture. With an 8-bit data bus and 8-bit data registers, it is referred to as an 8-bit architecture, e.g. B. MOS Technology 6502 or Zilog Z80 . Processors with different sizes of data bus and data registers are often referred to accordingly, e.g. B. the Motorola 68000 , which is referred to as a 16- / 32-bit processor with 16-bit data bus and 32-bit data registers. The currently ( 2013 ) newest processors are mostly 64-bit processors, e.g. B. AMD Opteron or AMD Bulldozer , or Intel processors with EM64T and (rarely) Itanium and Alpha AXP .

With 8-bit processors, the address bus and register were mostly 16 bits in size. In most processors today, the address registers are the same size as the data registers, and the address bus is usually the same size or smaller.

Most of the time the data registers are only connected to the ALU, but not to the FPU . That is, in most processor cores, data registers cannot be used as operands for FPU operations. In this case, operands for the FPU must be stored in specially designed registers, the floating point registers.

Freely usable registers

In modern RISC CPUs, such as PowerPC or Sun SPARC , the data registers are called general or freely usable registers (English GPR for General Purpose Register ), since they can be used as data or address registers . Similarly, the Motorola 68000 has eight equivalent data registers.

The 32-bit processors of the Intel x86 family come from a CISC architecture and therefore largely have the properties of their 8 and 16-bit previous generations . They only have four general registers, which are also referred to by the names from that time (accumulator, base register, counting register, data register). A processor core can also still not perform certain operations on all registers (e.g. divisions can only take place in the accumulator).

Address register

The address registers play an important role in address arithmetic. They are used to calculate memory addresses of operands or commands and are connected to the internal data bus and the address bus.

With indexed addressing , for example with the Intel 8086 , two types of address registers are distinguished:

- the base address registers (also segment registers ), which are discussed below under the special registers

- the index registers , which store the offset to a base address.

With linear addressing, for example with the Motorola 68000 , there is no such distinction. There is a type of addressing in which an address and a data register are added. With the Motorola 68020 , the data register can also be multiplied by a fixed word length.

In other processor architectures, the only register involved in addressing is called the index register: with the Motorola 6800 and the Zilog Z80 a constant is added, with the MOS Technology 6502 a 16-bit value and an 8-bit index register are added. The 6502 also has an addressing type in which one of several base address registers can be selected from a table stored in the RAM using an index register. The exact naming of the individual addressing types is inconsistent and processor-specific.

Special register

In addition to general registers, there are also special registers that store the operating status of the processor core and perform auxiliary functions for it. They can only be used for special operations (e.g. division) or they have very special functions ( interrupt descriptor table IDT, page table ...)

Special registers are only partially programmable by the user.

The following special registers can be found in most architectures:

- Command counter register , also program counter or command counter , (English Instruction Pointer IP ( 16-Bit ) or Extended Instruction Pointer EIP ( 32-Bit ) or program counter PC): Depending on the system architecture, contains the memory address of the current or the next command to be executed - a jump command sets this register to a new value

- Instruction register (English Instruction register ): saves the current command - for the programmer inaccessible

- Base register , e.g. B. for the base vector table: can be reset by a user program

- Segment register : a specialty of the x86 platform that contains the upper 16 bits of a 20-bit address; Their content must therefore be multiplied by 16 and then added to an offset within the segment in order to achieve the final memory address (in this way, 20-bit address space could be covered with pure 16-bit register load commands, i.e. 1 MiB )

- Status register (English: Condition Code Register CCR or Processor Status Word PSW or flag register ): indicates certain states after execution of a command (e.g. zero flag , sign flag etc.) - a user program initializes individual flags e.g. B. before arithmetic operations

- Interrupt control register (English: Interrupt Control Register ): When more complex CPUs where this functionality can not be dealt with (see above) with one or two bits in the status register, here above can be given a very differentiated, on which interrupts react at all and the priority with which shall be. By reading, the software can find out which of the various interrupts is actually present. By writing she can (temporarily) z. B. block individual interrupts that would interfere with a certain operation.

The refresh counter of the Z80, an automatic counter that generates the refresh addresses of the memory and is used by some programs as a pseudo-random number generator , also belongs to this category.

Some microcontrollers (Intel MCS 51 family and Siemens C167 family) organize these special registers and the registers for controlling the internal I / O ports in the form of a register bank that can be used with memory mapped I / O with the usual commands for can address the RAM access. The main memory hidden by this register bank can either not be addressed at all or only indirectly.

Stack register

The stack (also stack pointer or stack pointer from English stack pointer , short SP ) are address registers for managing stacks , and stack or just stack called.

A stack memory is organized by a stack register according to the LIFO principle and can be filled or emptied with push or pop operations. The stack register always points to the memory address at the end of the stack, depending on the architecture on or mostly behind the last element.

On most of today's architectures exist:

- a system stack that the operating system uses to save and restore the processor status when switching processes .

- a user stack ( call stack ) that can be freely used by the application program . When a subroutine ( procedure , subroutine ) is called, the return address is first noted on the stack at which the calling program is to be continued when the subroutine has ended. In addition, a separate stack area can be created dynamically for the call, return and local variables of the subroutine, which is released again after completion.

According to electrical typing

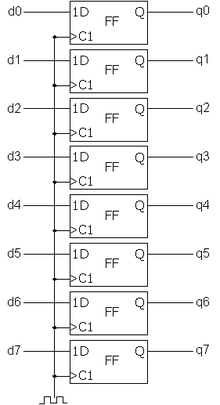

- simple latches that can store individual bits and output them for reading; these are most of the registers (status, parallel I / O data registers).

- Multi- bit counter registers , which also increase or decrease their content by 1 in response to a pulse; Examples: the program counter, the stack register and timer register.

- Shift registers are mainly found in the ALU of a CPU or a numerical coprocessor , where they perform sub-functions in multiplications and divisions, among other things .

Input / output register

In addition to buffer locations in the central processing unit of the computer system, registers can also appear in the electronics of connected peripheral devices or chips, but the CPU itself can also have integrated input / output registers. As a rule, they can be divided into the same sub-categories as the above. pure CPU register. A few representative examples:

- In addition to status and data registers, the status registers of the control units of the external mass storage usually include address registers that relate to the address information of the mass storage, today mostly sector numbers.

- In video chips, the bits in the status registers control e.g. B. the different video modes; Data registers can e.g. B. Sprite data included.

- With a parallel interface , a data register contains the actual print data and a status register contains the handshake bits. Often there is also a status register called DDR (for data direction register ), via which the data direction (input or output) of the data lines can be programmed (e.g. for bidirectional use).

These I / O registers can often also be accessed by the program of the central processing unit via port numbers as I / O ports or are mapped into the address space of the main memory ( memory mapped I / O ). Depending on the point of view, the conceptual distinction between memory locations in the RAM memory banks and register locations on logic modules has been retained.

history

Already in the first computer, the Zuse Z3 from 1941, and its predecessor, the Zuse Z1 from 1938, two memory locations "R1" and "R2" in the word size of the machine are available as operands for the arithmetic operations in the "arithmetic unit". Special machine commands are implemented for data exchange (loading and saving) between these registers and the storage unit, which can be seen separately from the arithmetic unit .

The development of the registers is therefore closely linked to the technical development of the working memory of the earliest computers: The first computers had no working memory at all in the current sense. All data and the program itself were stored on completely different media, such as mechanical memories, punch cards and magnetic drum memories. In order for the arithmetic unit to carry out an operation, words had to be transferred from the mass storage device to the arithmetic unit's buffer locations, which could then output a value to the switching logic. The value arising at the output of the switching logic had to be buffered again until it could be written to the mass memory. These buffer spaces were called registers (from Latin: regesta ; from regerere to enter).

It was recognized early on that the program flow could be optimized if you could buffer intermediate values over a few operations and add them up in the operation after that. Thus, individual registers became a set of registers, which at first also consisted of tubes or relays , but were then replaced by ferrite core memories with advancing technical development . The possible address calculation for the core memory led to a split of the terms - the naming as registers still means buffer locations, the location of which is hard-coded in the arithmetic unit's instruction code, while the core memory is indirectly addressed via index registers.

At the time of the core memory , the data values in the main memory were still linked directly to the arithmetic unit. In addition to arithmetic registers, the value of which went directly into the arithmetic logic, an instruction code contained the coded specification of index registers, the value of which was placed on the address lines of the core memory, and the outgoing value of the ferrite cores is then fed into the arithmetic logic. The core memory could have a few thousand places. With the ever faster arithmetic unit and the transition to cheaper but slower main memory based on capacitors (dynamic RAM), buffer spaces became necessary again, in which values from the main memory are first copied into register locations on the arithmetic unit in order to be processed from there.

Use in high-level languages

Some high-level languages such as C envisaged the explicit use of registers for variables which, according to the programmer, are used particularly frequently. Modern compilers (since the mid-1990s) ignore these attributes and leave the assignment of constants, variables or partial expressions to the optimizer .