Analog-to-digital converter

An analog-digital converter is an electronic device, component or part of a component for converting analog input signals into a digital data stream , which can then be further processed or stored. Other names and abbreviations are ADC , analogue-to-digital converter or A / D converter , English ADC ( a nalogue-to- d igital c onverter ) or shortly A / D.

A variety of repositioning methods are in use. The counterpart is the digital-to-analog converter (DAU).

Analog-digital converters are elementary components of almost all devices in modern communication and entertainment electronics, such as B. cell phones , digital cameras , or camcorders . They are also used to record measured values in research and industrial production facilities, in machines and everyday technical objects such as motor vehicles or household appliances.

Working method

An ADC converts a time and value-continuous input signal (analog signal) into a time-discrete and value-discrete sequence of digitally represented values. Due to a finite number of possible output values, quantization always takes place . The result of an AD conversion can be imagined in a signal-time diagram in a sequence of points with stepped horizontal and vertical distances. The main parameters of an ADC are its bit depth and its maximum sampling rate . The conversion time is usually much shorter than the reciprocal of the sampling rate.

The bit depth of an AD converter already limits the maximum possible accuracy with which the input signal can be converted. The usable accuracy is lower due to other sources of error in the ADC. In addition to the fastest possible methods, there are also slow (integrating) methods for suppressing interference.

Time discretization (sampling)

The minimum required sampling frequency for loss-free discretization results from the bandwidth of the input signal.

In order to be able to completely reconstruct the signal later, the sampling frequency must be greater than twice the maximum possible frequency in the input signal (see Nyquist frequency ). Otherwise, there is a sub-sampling and leads in the reconstructed signal to the input signal is not existing frequencies. Therefore the input signal must be band-limited . Either it is this on its own or it is made into such a signal by low-pass filtering .

Sometimes, however, the signal to be sampled is so high-frequency that this condition cannot be technically implemented. However, if the input signal is periodic, a reconstruction can still be made possible by multiple sampling with a time offset without violating the sampling theorem, since intermediate points are determined when the signal is passed through several times and a larger number of interpolation points is created, which in the end results in an increase in the Sampling rate.

In many conversion processes, the input signal must not change during signal conversion. Then switch to the actual AD converter, a sample and hold circuit (sample and hold) before which the signal value ( English sample ) analog so caches that it remains constant during quantization. This is especially true of the step-by-step and bit-wise converters, which require longer conversion times. If a converter requires this sample-and-hold circuit, it is usually included when it is implemented as an integrated circuit .

In many applications, the input signal should always be sampled at exactly the same time intervals. However, due to random variations in the distances, an effect occurs that is known as jitter . It falsifies the original signal during the later reconstruction, since this is again equidistant - that is, with the same time intervals.

The conversion time must not be confused with the latency of a converter, i.e. H. the time that elapses after the acquisition until an AD converter has passed on the date. This time can be much longer than the conversion time, which can be particularly disruptive in control technology. It is caused by pipelining of the converter, post-processing of the data and the serial data transmission .

Quantization

The quantization of the previously time-discrete signal represents the actual transition from an analog signal to a digital signal. Due to the finite bit depth of the converter, there is only a certain number of code words and their associated input voltage. The signal is quantized. The deviation between the true input voltage and the quantized input voltage is called the quantization deviation . The more bits or code words that are available, the smaller this unavoidable deviation. In an ideal AD converter, each additional bit reduces this noise by 6.02 dB. With real AD converters, the effective number of bits (ENOB) can be used to estimate what a further bit would bring in the converter under consideration (for example, a further bit in a 12-bit converter with an ENOB of 11 bits would be approx , 15 bit or 0.9 dB).

The ratio of the maximum possible undistorted input voltage and the noise with a signalless input is called the dynamic range . Converters that deliver a constant code word in the absence of an input signal have an infinitely high dynamic range. It makes more sense to specify the signal-to-noise ratio (or the SINAD , signal to noise and distortion ratio, ratio of the signal to the sum of noise and distortion).

Reference value

Since the analog signal fed to the ADC is converted into a variable digital value, it must be evaluated with a specified value or signal (input signal range or measuring range ). In general, a fixed reference value (e.g. an internally generated reference voltage) is used. The analog input signal is mapped digitally, the reference defines the permissible peak value of the input signal.

Quantization characteristic

In analog-digital converters, there is always a non-linear relationship between the input and output variables . However, if the digital value changes at constant intervals with increasing input voltage or if the characteristic curve approaches a straight line with extremely fine gradations, one still speaks of a linear analog-digital converter. There are

| unipolar versions, for example in the dual system | ||

| 000… 000 for 0 | 100… 000 for / 2 | 111… 111 for - 1 LSB |

| bipolar versions, for example in the dual system with offset | ||

| 000… 000 for / 2 | 100… 000 for 0 | 111… 111 for / 2 - 1 LSB |

other codings, for example two's complement , BCD code, can also be used.

Interfaces

In addition to the sample-and-hold circuit already mentioned , additional circuits are required for the interface to the analog world, so that these are often integrated on a chip together with the actual converter. These can be, for example, buffer or amplifier circuits, possibly with switchable gain ( Programmable Gain Amplifier (PGA)) and inputs for differential signal transmission . There are also variants without a real subtraction amplifier at the input; Instead, the two lines of the differential signal are processed one after the other and only then is the difference formed (so-called pseudo differential inputs ).

Digital data is made available at the output. Classically, each bit of the output variable appears on its own connection pin; the size is output in parallel - not to be confused with the parallel conversion . If the size is to be displayed on a display , integrated seven-segment encoders are also used, or the size is output as a BCD code in a multiplex process . The disadvantage of the parallel output, especially when further processing by microprocessors or controllers , is the large number of connection pins required. Therefore serial connections are often implemented, for example with the protocols I²C , SPI or I²S . With appropriate data rates, LVDS or JESD204B technology is used , for example .

Deviations

In addition to the unavoidable quantization error, real AD converters have the following errors:

Zero point errors, gain errors and non-linearity errors

The following errors are defined as deviations in the characteristic curves between the real and ideal converter (see figure):

- Zero point error (offset)

- Gain error ( english error gain )

- Non-linearity error

The gain error is often given as a fraction of the current value, the zero point error together with the quantization error and the non-linearity error as fractions of the final value or as a multiple of an LSB.

Error in the graduation

Individual steps can be of different widths.

With a continuously increasing input variable, depending on the implementation method, it can happen that a value of the output variable is skipped, especially when there is a carry over several binary digits, for example from 0111 1111 to 1000 0000. This is called “missing codes”.

Temporal and aperture errors

When every non-constant input signal is converted, fluctuations in the converter clock Δ t ( clock jitter ) result in an error proportional to the change in the input signal over time. In the case of a sinusoidal signal of frequency f and amplitude A, it is . Any jitter creates additional noise - there is no threshold below which there is no deterioration in the signal-to-noise ratio. Many current converters (especially delta-sigma converters) have internal clock processing. The reason for this is that many converters require a higher internal clock rate or, in the case of delta-sigma converters, that jitter there directly (i.e. even with a constant input signal) causes conversion errors.

Implementation process

There are a large number of methods that can be used to convert analog to digital signals. The following are the main principles. In all examples, the electrical voltage is used as the input variable.

The blocks themselves control the internal process of a conversion. For the cooperation with a computer, an ADC can be provided with a start input for the request for a new conversion, with a “busy” output for the notification of the ongoing conversion and with bus-compatible data outputs for reading out the resulting digital value.

Integrating converter (counting method)

There are two processes involved in these procedures:

- an analog process influenced by the measured variable, in which a capacitor is continuously charged and discharged again alternately,

- a digital process that measures times or pulse densities depending on the charging process, which is counted.

The follow-up converter also counts. This is operated without a capacitor as a feedback converter and is explained further below.

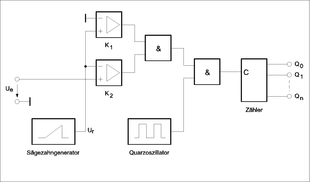

Single-slope converter (sawtooth / single ramp method)

In the sawtooth method, the output voltage of a sawtooth generator is compared with the ground potential (0 V) and the ADC input voltage via two comparators K 1 and K 2 . During the period in which the sawtooth voltage passes through the range between 0 V and the voltage , the pulses of a quartz oscillator are counted. Due to the constant slope of the sawtooth voltage, the elapsed time and thus the counter reading when reaching is proportional to the level of the ADC input voltage. At the end of the counting process, the counting result is transferred to a register and is available as a digital signal. The counter is then reset and a new translation process begins.

The conversion time for this ADC depends on the input voltage. Rapidly changing signals cannot be captured with this type of converter. Converters using the sawtooth method are imprecise, as the sawtooth generator works with the help of a temperature and age-dependent integration capacitor. Due to their relatively low circuit complexity, they are used for simple tasks, for example in game consoles, in order to digitize the position of a potentiometer that is moved by a joystick or a steering wheel.

Dual and Quadslope converter (multi-ramp method)

Dual and quad slope converters essentially consist of an integrator and several counters and electronic switches . The integrator works with an external, high-quality capacitor that is charged and discharged in two or more cycles. With the two-ramp procedure (dual slope), the integrator input is first connected to the unknown ADC input voltage, and charging takes place over a fixed time interval. For the subsequent discharge, the integrator is connected to a known reference voltage of opposite polarity. Details are explained under digital metrology . The required discharge time to reach zero voltage at the integrator output is determined by a counter; the meter reading directly represents the input voltage if dimensioned appropriately. With this method, the size of the capacity is reduced from the result. In order to correct the zero point error of the ADC, a further charge / discharge cycle is carried out with the integrator input short-circuited with the four-ramp method. The reference voltage is the determining factor for the accuracy; this means, for example, that thermally induced fluctuations must be avoided.

Such converters based on the multi-ramp method are slow, do not require a sample-and-hold circuit and offer high resolution as well as good differential linearity and good suppression of interference signals such as noise or network coupling. The typical area of application are display measuring devices ( digital multimeters ) which hardly need a conversion time of less than 500 ms and can eliminate superimposed 50 Hz disturbances of the mains frequency with a suitable integration time.

Charge balance converter

In the charge balancing process, the capacitor of an integrator is charged by an electric current proportional to the input variable and discharged by short current surges in the opposite direction so that no charge builds up on average. The greater the charging current, the more frequently it is discharged. The frequency is proportional to the input variable; the number of discharges in a fixed time is counted and provides the digital value. In terms of its behavior, the procedure is similar to the dual slope procedure. Other analog input stages that contain a voltage-frequency converter with sufficient high-quality accuracy also lead to a digital value via a frequency count.

Feedback converter (serial process)

These work with a DAU that provides a comparison value . This is approximated to the analog input signal using a suitable strategy . The digital value set at the end on the DAU is the result of the ADC. Since the process requires a period of time in which the input signal must not change, a sample is taken from it by means of a sample and hold circuit (S / H) and recorded during the implementation.

Follow-up relocator

Here a counter is used as a data memory. Depending on the sign of , the system counts up or down by one step and then compares it again - counts and compares it again until the difference is smaller than the smallest adjustable step. These converters simply “follow” the signal, whereby the conversion time depends on the distance between the current input signal and the signal during the last conversion.

Successive approximation

These work with a DAU that builds up a comparison value every time. The input signal is limited by nesting intervals . Simple successive approximation converts one bit per step. A conversion that is orders of magnitude more precise and faster can be achieved in that the conversion is carried out redundantly by converting with a smaller step size than corresponds to one bit.

Weighing method

One possible approximation method is the weighing method . First, all bits are set to zero in a data memory ( successive approximation register , SAR). Beginning with the most significant bit ( Most Significant Bit , MSB) to the least significant bit will be down to least significant bit (LSB) determined one after the other all the bits of the digital value.

The control unit sets the bit in progress to one on a trial basis; the digital-to-analog converter generates the comparison voltage corresponding to the current digital value. The comparator compares this with the input voltage and causes the control unit to reset the bit in progress to zero again if the comparison voltage is higher than the input voltage. Otherwise the bit is at least necessary and remains set. After setting the least significant bit is smaller than the smallest adjustable step.

The input signal must not change during the conversion , since otherwise the lower-order bits would be obtained on the basis of the higher-order bits that were determined but no longer valid. Therefore a sample-and-hold circuit (S / H) is connected upstream of the input. The ADC needs one clock cycle conversion time for each bit of accuracy. Such converters achieve resolutions of 16 bits at a conversion rate of 1 MHz.

Redundant converters

Redundant analog-to-digital converters similar to the weighing process assume that there is no exact halving of the still open interval around the target value, but that this interval is only limited by a portion thereof. To do this, they have a digital-to-analog converter, the elements of which are not graded according to the dual system, i.e. always by a factor of 2, but by a smaller factor. On the one hand, you accept that more elements are required to cover the same range of values, but on the other hand, you allow the converter to work an order of magnitude faster and achieve an accuracy that is several orders of magnitude higher: The faster function comes from the fact that the comparator In each step there is no need to wait until its amplifier has settled up to a multiple of the target accuracy (always on the order of magnitude as many settling time constants as the converter is supposed to convert bits), but rather make a decision after the short 50 percent settling time which is then faulty in a fairly large area within the remaining interval. However, this is more than compensated for by the redundantly designed converter elements. The total conversion time of such a converter is in the order of magnitude a power of ten below that of its simple model. Due to the redundant implementation process, such a converter has a much lower level of inherent noise than its purely dual counterpart.

In addition, such an ADC can calibrate itself up to an accuracy that is only limited by the noise. By letting the self-calibration run much more slowly than the implementation in the practical application, the influence of noise in this process can be reduced by an order of magnitude. The resulting characteristic of such a converter is absolutely linear apart from a noise-like deviation of a few multiples of the smallest element used for self-calibration. By placing two converters of this type next to each other on the same chip and one always in the calibration mode, converters of this type can be made almost resistant to manufacturing tolerances, changes in temperature and operating voltage. The achievable resolution is exclusively noise-limited.

Delta-Sigma method

The delta-sigma method, also known as a 1-bit converter, is based on delta-sigma modulation . In the simplest form (first-order modulator), the input signal comes to the integrator via an analog subtracter and causes a signal at its output, which is weighted with one or zero by a comparator. A flip-flop generates a discrete-time binary signal with which a 1-bit digital-to-analog converter supplies a positive or negative electrical voltage, which pulls the integrator back to zero via the subtractor ( control loop ). A downstream digital filter converts the serial and high-frequency bit stream into data with a low refresh rate, but a large bit width (16 or 24 bits) and a high signal-to-noise ratio (94 to 115 dB). In practice, delta-sigma converters are constructed as third or fourth order systems, that is to say by means of several serially arranged differential and integrator stages. This allows better noise shaping and thus a higher gain in resolution with the same oversampling.

One advantage of the delta-sigma converter is that the dynamics can be interchanged within certain limits due to the bandwidth. Due to the continuous sampling at the input, no sample and hold circuit is required. In addition, low demands are made on the analog anti-aliasing filter.

The advantages come at the price of the disadvantage of the comparatively high latency period, which is mainly due to the digital filter stages. Delta-Sigma converters are therefore used where continuous signal curves and only moderate bandwidths are required, such as in the audio sector. Practically all audio devices in the field of entertainment electronics, such as DAT recorders , use these converters.

It is also increasingly used for data converters in communication technology and measurement technology due to falling prices. However, due to the high oversampling required in this case, there are limits to the method at higher frequencies. The limit is around 2.5 MHz.

Parallel converter

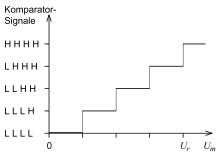

Single-stage parallel converters (flash converters)

While the successive approximation carries out several comparisons with just one comparator, the direct method or Flash implementation can do with just one comparison. In the case of flash converters, however, a separately implemented comparator is required for each possible output value (except for the largest). For example, an 8-bit flash converter therefore requires 2 8 −1 = 255 comparators.

The analog input signal is simultaneously compared in the flash converter by all comparators with the comparison values (generated by a linear voltage divider). This is followed by a code conversion of the 2 n −1 comparator signals into an n bit wide binary code (with n : resolution in bits). The result is immediately available after the throughput delays (switching time of the comparators and delay in the decoding logic). As a result, the flash converters are very fast, but generally also involve high power losses and acquisition costs (especially with the high resolutions).

Regardless of the resolution, the code conversion only requires one column with AND gates and one column with OR gates (see picture). It converts the result of the comparators into a binary number. It works with a very short transit delay that is the same for all binary digits. Three comparators are required for the four possible values of a two-bit converter. The fourth only has the function of signaling that the measuring range has been exceeded and supporting code conversion.

Multi-stage parallel converters (pipeline converters)

Pipeline converters are multi-stage analog-to-digital converters with several independent stages that are constructed in a pipeline architecture . Their stages usually consist of flash converters over a few bits.

A rough quantization is carried out in each pipeline stage, this value is converted into an analog signal with a DAC and subtracted from the buffered input signal. The residual value is increasingly fed to the next stage. The advantage lies in the greatly reduced number of comparators, e.g. B. 30 for a two-stage eight-bit converter. Furthermore, a higher resolution can be achieved. The multistage increases the latency but does not significantly reduce the sampling rate. The pipeline converters have replaced the real parallel converters except for extremely time-critical applications. These multi-stage converters achieve data rates of 250 MSPS (Mega Samples Per Second) with a resolution of 12 bits (MAX1215, AD9480) or a resolution of 16 bits with 200 MSPS (ADS5485).

The values of the quantization levels are added, taking their weighting into account. Most of the time, a correction ROM also contains calibration data which are used to correct errors that arise in the individual digitization stages. In some versions, these correction data are also generated in response to an external signal and stored in a RAM .

Pipeline converters are typically used in all digital oscilloscopes and when digitizing video signals. As an example, the MAX109 enables a sampling rate of 2.2 GHz with a resolution of 8 bits. In the meantime, however, there are even faster (4 GSPS) and more precise converters (16 bit @ 1 GSPS). In today's digital oscilloscopes with possible sampling rates of 240 GSPS, demultiplexers are also connected upstream.

Hybrid converter

A hybrid converter is not an independent converter, but rather it combines two or more conversion methods, for example based on a SAR structure, with the original comparator being replaced by a flash converter. As a result, several bits can be determined simultaneously in each approximation step.

Market situation

There are essentially four processes on the market:

- Pipeline converters are used for high sampling rates. Speeds 40 MSPS to 5 GSPS. Usual dynamics 8 bit, 12 bit (up to 4 GSPS) or 16 bit (up to 1 GSPS).

- If high accuracy with moderate sampling rates is important and latency is not an issue, sigma-delta converters are used. Speeds from a few PLCs to 2.5 MSPS. Bit depths 16 bits to 24 bits.

- If the latency is significant or interferes with the comparatively steep low-pass behavior, successively approximating converters are used. Speeds 0.1 MSPS to 10 MSPS.

- In simple display measuring devices such as multimeters, counting methods that dampen slow interference, such as dual-slope converters, are used.

With this procedure you can cover almost all practical requirements and with moderate requirements (e.g. 12 bit, 125 KSPS, 4 channels) these converters can be obtained inexpensively (approx. 1 €).

Important parameters

- Sampling (sample rate) - indication of the frequency of transposition.

- Resolution (Resolution) - width of the steps (even number of stages, or number of points), which are used to display the output signal.

- Zero point error - The converter characteristic (without taking the graduation into account) is shifted. The digital value differs from the correct value by a constant amount.

- Sensitivity error , gain error - The converter characteristic (without taking the gradation into account) is twisted (slope error). The digital value differs from the correct value by a constant percentage of the input variable.

- Integral non-linearity - the error due to the fact that a converter characteristic curve, which is taken as a linear basis (without taking the gradation into account), is not straight.

- Differential non-linearity - deviation of the width of the conversion stages from one another

- Quantization curve - graphical representation of the relationship between the digital output values and the analog input values, e.g. B. following a linear or logarithmic course.

- Quantization error - Due to the limited resolution, the output signal deviates from the functional (continuous) curve.

- Information gap (missing code) - If a continuous increase in the input signal does not result in consecutively numbered values of the output code, but rather a value is skipped; possible with a differential non-linearity of more than 1 LSB.

- Latency - propagation delay from the acquisition of the input signal to the provision of the associated output signal.

- Signal-to-noise ratio in dB

- Dynamic range in dB

- Dynamic parameters

- Intermodulation interference in dB

- Operating current - the faster the converter electronics have to work, the higher its supply current (self-heating).

See also

- Antialiasing (signal processing)

- Dithering (audio technology)

- Digital measurement technology

- Multichannel analyzer

- List of audio terms

literature

- Rudy J. van de Plassche: CMOS integrated analog-to-digital and digital-to-analog converters. 2nd edition. Kluwer Academic, Boston 2003, ISBN 1-4020-7500-6 (English)

- Ulrich Tietze, Christoph Schenk: Semiconductor circuit technology. 12th edition. Springer, Heidelberg 2002, ISBN 3-540-42849-6

- Rüdiger Klein, the new workbook electronics. Bercker, Kevelaer, ISBN 978-3-645-65094-6

Web links

- Literature on analog-digital converters in the catalog of the German National Library

- Basics based on simulations

- An introduction to delta-sigma converters

- AD converter in "Applied Microelectronics" - Basics

- Pipelined Subranging ADCs (PDF; 1 MB)

Individual evidence

- ↑ Of the common terms that is used here that has been defined for engineering by standardization in DIN 1319-2 .

- ↑ Application Note 1108 - Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs , application note by Maxim Integrated , 2002-006-14, accessed on 2018-12-12

- ↑ Data sheet of the MAX109 flash converter (PDF; 452 KiB).