Flash memory

Flash memories are digital memory modules for non-volatile storage without maintenance energy consumption. The exact name of this type of memory is Flash-EEPROM . In contrast to normal EEPROM memory, bytes (usually the smallest addressable memory units) cannot be individually deleted or overwritten. Flash memories are slower than read only memory (ROM).

history

Designation and name

The term flash was according to a story from the development laboratory of Toshiba in 1984 as follows: Shoji Ariizumi , an employee of the project manager Fujio Masuoka , the memory felt by the block-wise working erasing a flash ( English flash ) reminiscent of a camera, so he flash the name proposed.

Development history

The EPROM was developed by Dov Frohman at Intel. Intel brought the 2- Kibit EPROM "1702" onto the market in 1971. The first commercial microprocessor i4004 from Intel (1971) would have been less successful without the EPROM as a program memory .

However, the 1702 EPROM had to be removed for deletion and irradiated with UV light . In 1978 Perlegos developed the 2816 chip: the first EEPROM memory that could be written to and erased without a quartz window .

NAND flash memory was developed by Toshiba from 1980 (published 1984), NOR flash from 1984 by Intel (published 1988). In the following year, 1985, the first solid state disk ( SSD for short ) was installed in an IBM personal computer . However, this technology was so expensive at the time that it was only of interest to the military.

The history of flash memory is closely related to the history of the digital camera . The first CompactFlash medium with a capacity of four megabytes was introduced by SanDisk in 1994 . When M-Systems launched a solid state disk in 1996, the flash memory became interesting for private users. In 1998 Sony introduced the first memory stick , these were also used in older versions of the PlayStation .

Flash memories are used wherever information has to be stored non-volatile ( persistent ) in the smallest of spaces - without permanent supply voltage. This also includes memory cards for digital cameras and other mobile devices such as cell phones , smartphones and handhelds . Other designs or devices in which this storage technology is used are USB sticks and MP3 players as well as the already historic DiskOnChip . The latter were used, for example, for the permanent storage of firmware in many devices with microcontrollers ( embedded systems , BIOS ); for the same purpose, increasingly integrated on the microcontroller itself: embedded flash .

The use as the main mass storage medium in computer systems is of increasing interest . Here Flash Memory may take the form of solid-state drives (dt. Solid state drive), the conventional magnetic hard drives (English hard disk drive replace or supplement (see.) Hybrid hard drives ).

Working principle

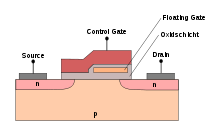

In a flash EEPROM memory information (to be bits ) in a memory unit (memory cell) in the form of electric charges on a floating gate or a charge trapping memory element of a metal-insulator-semiconductor field effect transistor ( English Metal Insulator Solid State Field Effect Transistor, MISFET ). In both cases, the charges on the gate (stationary space charges), as with normal MISFETs, influence the charge carriers in the area below between the source and drain contact (the so-called channel), which influences the electrical conductivity of the field effect transistor and thus permanent information storage becomes possible.

Unlike the gate in normal MISFETs, the floating gate is electrically isolated from all other parts (channel region and from the control gate) by a dielectric (currently mostly silicon dioxide ); the potential on the floating gate is therefore undefined basically (this is also called floating , English floating , hereinafter). In a charge-trapping memory which takes over an electrically non-conductive layer of silicon nitride , the electron and hole are at bonding locations (English trapping center ) held stationary. Although the two variants have clear differences in the structure, the functional principle with stationary electrical charges, which influence a MISFET in its properties, is the same in both cases.

In order for information to be stored in a targeted manner, however, it must be possible to bring charges to the floating gate or charge trapping structure and remove them again. This change in the state of charge is only possible through the quantum physical tunnel effect , which allows electrons to pass through the actual dielectric. However, since this can only take place through large differences in the electrical potential across the insulator (which represents a potential barrier for charge carriers), the electrical insulation of the floating gate means that charges cannot flow away from the floating gate and the memory transistor retains its information for a long time .

In the early stages of this technology, only two charge states were distinguished, so only one bit could be stored per cell. In the meantime, however, Flash EEPROM memories can store several bits per memory transistor (e.g. MLC memory cell , TLC memory cell ); For this purpose, floating gates use the different electrical conductivity at different charge states of the transistor and, with charge trapping, the possibility of storing one bit of information separately in the drain and in the source region. The two bits per MISFET are read out by changing the direction of the readout current in the channel.

Save and read

The storage of a bit - in the following only the storage process for a floating gate is shown - takes place via the floating gate , the actual storage element of the flash field effect transistor. It lies between the control gate and the source-drain path and is insulated therefrom as well as from the control gate by means of an oxide layer. In the uncharged state of the floating gate, if the control gate controls the transistor to “open”, a current can flow in the source-drain path (channel). If electrons are brought to the floating gate via the control gate by applying a high positive voltage (10–18 V), no more current can flow in the source-drain path even when the transistor is actually switched to "open" negative potential of the electrons on the floating gate counteracts the voltage at the control gate and thus keeps the flash transistor closed.

The uncharged state is achieved again in that the electrons are driven out of the floating gate again by applying a high negative voltage via the control gate channel path. It is even possible that the flash transistor switches to the normally on state, i.e. In other words , it conducts current even when there is no voltage at the control gate ( over erase ): instead of electrons, the floating gate is now virtually occupied with positive charge carriers ( defect electrons , "holes"). This is particularly problematic in NOR architectures (see below).

Note: Whether the charged or uncharged floating gate state is viewed as a 0 or 1 state of the memory cell is implementation-dependent. By convention, however, that state of the floating gate that is established by erasing blocks by block is usually referred to as 0 ("erased"). Correspondingly, the bit-by-bit adjustable state is referred to as 1 (“programmed”).

Tunnel effect

The mechanism by which the electrons pass through the insulating oxide layer is called the Fowler-Nordheim tunnel effect (after their first explorers). In other words , a flash memory is the application of an effect that can only be interpreted in terms of quantum mechanics . To increase the likelihood that electrons tunnel to the floating gate, the CHE ( channel hot electron ) procedure is often used: the electrons are accelerated by applying a voltage across the channel, i.e. between the drain and source, and thus to one higher energy level (hence hot ), whereby they tunnel between gate and channel to the floating gate even at lower voltages (typically 10 V). (In the programming illustration above, this procedure is indicated - but for an older technique.)

Control

A flash memory consists of a certain number of individual memory elements depending on the memory size. The bytes or words (typically up to 64 bits) can be addressed individually. In some architectures they can also be written individually, whereas in others only larger amounts of data can be programmed at once. As a rule, the opposite operation, deletion, is possible, but only in larger units, so-called sectors (usually a quarter, eighth, sixteenth, etc. of the total storage capacity). The logical polarity is not always the same: There are implementations that implement programming as a logical transition from 0 to 1, and vice versa.

However, the common feature is that the two operations:

- only represent the transition in one direction (0 to 1 or 1 to 0) and

- (often) only one of the two can work bit-selectively: programming.

This means that an erase operation (on a byte in some EEPROM architectures, on a sector in Flash) is always necessary for rewriting and then the desired bit pattern, i.e. the desired memory content, is created by programming operations.

Often, special commands (in the form of a sequence of precisely specified data / address pairs to be created) must be given to the flash memory in order to write to the flash memory. This is a security measure against unintentional writing or deletion of the memory.

All of these detailed operations are usually carried out transparently for the user and the respective application program. Most of the time, there are file systems optimized for flash memory that implement these practices. Some flash memories, such as USB sticks , also have their own microcontroller to operate the interface to the computer , on which wear-leveling algorithms are implemented that ensure that the data carrier is worn as evenly as possible even without such an optimized file system.

Architectures

As of 2005, two flash architectures are common on the market, which differ in the type of internal interconnection of the memory cells and thus in the storage density and access speed. In principle, the memory cells are arranged as a matrix, with the address lines serving to select a column or row of memory cells via one coordinate and data lines leading to the memory cells in the other coordinate. The implementation of the data lines represents the essential difference between the NAND Flash and NOR Flash architectures.

NAND flash

The memory cells are connected in series in larger groups (e.g. 1024) (series connection). This corresponds to the n-channel branch of a NAND gate in CMOS technology. Each group shares one data line. Reading and writing is therefore not possible randomly, but must always be done sequentially in whole groups. Due to the lower number of data lines, NAND Flash requires less space. Since data is also read in blocks on hard disks, NAND flash is suitable as a replacement for disk storage despite this limitation.

The NAND architecture is aimed at markets in which a lot of memory in a small space is important, but less important is low access time.

NOR flash

The memory cells are connected in parallel via data lines - these can be on the source or drain side depending on the exact architecture. This corresponds to an interconnection as in the n-channel branch of a NOR gate in CMOS. Access can be made here freely and directly. This is why the program memory of microcontrollers is built from NOR Flash.

The NOR architecture relies on the replacement of UV-erasable EPROMs (which in the meantime have almost been replaced by flash components and are hardly further developed). In addition, significantly shorter access times can be achieved here: The parallel connection has the lower resistance between the current source and the evaluation circuit.

Disadvantages of both architectures

Flash memories have a limited service life, which is specified in a maximum number of erase cycles (10,000 to 100,000 cycles for NOR flash and up to two million for NAND flash). At the same time, this corresponds to the maximum number of write cycles, since the memory must be erased in blocks before it can be written to again. This number of cycles is called endurance . This limited service life is due to the occurrence of damage in the oxide layer in the area of the floating gate, which causes the charge to flow away.

Another important parameter is the time of error-free data storage, retention .

Another disadvantage is that write access to flash memory is considerably slower than read access. Additional delays can result from the fact that only whole blocks can be deleted.

techniques

The most important criterion for differentiating between flash technologies is the geometry of the memory cell, the flash transistor, among other things, the following cell types are distinguished (several of the following features can apply at the same time):

- the split gate cell

- the ETOX cell, a simplified structure in which the downward kinking part of the control gate of the split-gate cell is omitted, the floating gate of which is usually charged with CHE

- the UCP cell ( uniform channel program ), which is usually described in both directions with Fowler-Nordheim tunneling

- the NROM cell in charge-trapping memories : here the charge is “shot” directly into a zone of the silicon nitride insulator between the channel and the control gate, even in versions with two charge zones (one in the source, the other in Drain near), which allows this cell to store two bits at a time. Common for larger NAND memories in the form of vertical NAND structures (V-NAND), which have been available since 2002.

- the two-transistor cell: a normal n-channel transistor and a flash transistor in a row. This cell has the disadvantage that it is larger, but in certain circumstances it can be controlled more easily for programming and erasing, which can result in area savings in other circuit parts with smaller memory sizes.

- Multi-level cell : Here the flash cell not only stores one bit, but (mostly) two, now four independent bit states. These are encoded in conductivity values, which are distributed to the two bits in the readout electronics. The factual doubling of the storage capacity is, however, due to the significantly longer access time (an analog voltage must be checked at four levels compared to only two for the binary flash cells) and a greater probability of errors (a change in conductivity by one sixteenth of the maximum conductivity difference can already reduce the value of the change the levels stored in the cell).

Storage sizes

At the beginning of 2009 several manufacturers (Samsung, Toshiba and others) delivered NAND flash memories with 16 gigabytes in SLC technology ( single level cell ) and 32 gigabytes in MLC technology ( multi level cell ), NOR flash memory reached at the same time Time 1 gigabyte of storage capacity.

The main result of the difference in storage capacity is that in NAND flash memory, the data and address lines are carried out on the same connections (pins). In other words, the same connection is used alternately for data and address transmission (“multiplex”), while these are separate for NOR flash memories. This means that the NOR types can access data much faster, but have significantly more pins and therefore generally require larger housings. De facto, however, with high capacities, the housings of the NAND types are almost as big as those of the NOR types, but this is due to the very large memory chip inside, not the space requirements of the connections. Even so, very few housing pins are actually connected with NAND types, so the advantage of the simpler “wiring” of the component in the device is retained.

The NAND Flash SSDs available as of 2019 are between 128 GB and 4 TB in size.

Number of erase cycles

The maximum number of erase cycles of flash memories varies depending on the manufacturer, technology (MLC or SLC-NAND, NOR) and structure size (50 nm, 34 nm, 25 nm). The manufacturer's specifications range from 3,000 to several 100,000. Micron Technology and Sun Microsystems announced in 2008 the development of an SLC NAND flash memory with a life expectancy of 1,000,000 cycles.

The flash memory stores its information on the floating gate. During an erase cycle, the electrons tunnel through the oxide layer. This requires high voltages. As a result, the oxide layer surrounding the floating gate is slightly damaged (degeneration) with every erasure process. At some point the oxide layer no longer provides insulation, the electrons no longer remain trapped on the floating gate, and the information stored on the memory cell is lost. However, the failure of a single cell does not make a flash memory unusable.

Defect management in flash / control logic

Failures of individual cells are recognized by an error detection and logged in a protected area. For error detection and correction, additional bits are stored for each block (512 bytes) . With these protection bits, individual faulty bits can be corrected, errors over several bits are not reliably detected. The control logic shows errors in this block, the driver software can then mark these blocks as defective. This defect table is located in the so-called spare (reserve) area of the flash, which is not written to during normal operation. The calculation and control of the protection bits is implemented in the control logic, not in the flash itself. In addition to simple Hamming codes , BCH codes and Reed-Solomon codes are mainly used .

Defect management through software

In order to avoid such defects, the driver software is designed in such a way that it distributes the write and delete actions as evenly as possible over the entire memory area of a module and, for example, does not always start writing at address 0. One speaks of wear leveling algorithms (German: algorithms for uniform wear).

Advantages and disadvantages

As a non-volatile storage medium, flash memory competes primarily with hard drives and optical storage media such as DVDs and Blu-ray discs .

A major advantage lies in the mechanical robustness of flash memory. In contrast, hard drives are very sensitive to shock ( head crash ). The lifespan of the plug contacts ( USB plug) is often the limiting factor .

Another advantage is the permissible higher ambient temperature , whereby the operating temperature of the storage element with a maximum of 100 ° C is lower than with modern magnetic layers of a hard disk (greater than 100 ° C).

Since a flash memory does not have any mechanically moving parts, it offers a number of advantages over other fixed memories: Both energy consumption and heat generation are lower. In addition, the memory works silently and is largely insensitive to vibrations. The implementation as a semiconductor memory results in a low weight and a small design. A 16 GB microSD card including plastic housing and controller achieves a data density of 139 GB / cm³. The access times are very short compared to other permanent storage devices. This not only improves performance, it also opens up new fields of application. For example, a flash memory is used as a fast buffer, for example as a ReadyBoost cache. The minimum costs per storage system can be lower compared to hard disks, for example with cheap netbooks .

Flash technology cannot compete with volatile memory such as RAM ( Random Access Memory ), as the data rates that can be achieved with Flash are significantly lower. In addition, the access time with NAND flash for read and write access is significantly longer. With NOR flash, this only applies to write access. The costs per gigabyte are significantly higher for flash memory than for hard drives and optical discs. A major problem with flash memory is its susceptibility to errors. Sectors are mainly damaged by erase accesses, over time they become indescribable and therefore defective (see number of erase cycles ). Irrespective of this, permanent bit errors can occur. All these errors can be hidden by suitable error correction measures, but this is expensive and increases the complexity of the flash controller. However, a flash memory cannot be prevented from becoming smaller over time as the number of usable sectors decreases. Compared to the lifespan of a hard drive, however, this effect is negligible.

literature

- Boi Feddern, Benjamin Benz: Memory cards / FAQ - Flash durability . In: c't . No. 2. , 2007, ISSN 0724-8679 , p. 168 .

Web links

- Algorithm to replace EEPROM by flash memory (English)

- Basics of flash technology Technical article on Storage-Insider.de

Individual evidence

- ↑ Vojin G. Oklobdzija: digital design and fabrication . CRC Press, 2008, ISBN 978-0-8493-8602-2 , pp. 6-4 ( limited preview in Google Book search).

- ↑ spectrum.ieee.org: Remembering the PROM knights of Intel , George Rostky, July 3, 2003

- ↑ spectrum.ieee.org: 25 Microchips That Shook the World , Brian Santo, May 1, 2009

- ↑ http://www.storagesearch.com/chartingtheriseofssds.html

- ↑ P. Pavan, R. Bez, P. Olivo, E. Zanoni: Flash Memory Cells - An Overview . In: Proceedings of the IEEE . tape 85 , no. 8 , 1997, ISSN 0018-9219 , pp. 1248–1271 , doi : 10.1109 / 5.622505 ( PDF (500 kB) ). PDF (500 kB) ( Memento of the original from April 26, 2014 in the Internet Archive ) Info: The archive link was inserted automatically and has not yet been checked. Please check the original and archive link according to the instructions and then remove this notice.

- ↑ Benjamin Benz: Memory Cards - The Technology of Flash Memory Cards . In: c't . No. 23 , 2006, ISSN 0724-8679 , p. 136 ff . ( Reading excerpt ( memento from November 17, 2006 in the Internet Archive )).

- ↑ Samsung moves into mass production of 3D flash memory . Gizmag.com. Retrieved August 27, 2013.

- ↑ Christof Windeck: MirrorBit Quad: four bits per flash memory cell. In: Heise-Online. September 26, 2006, accessed March 27, 2009 .

- ↑ Micron Collaborates with Sun Microsystems to Extend Lifespan of Flash-Based Storage, Achieves One Million Write Cycles . Micron Technology, Inc. December 17, 2008.

- ↑ Benjamin Benz, Boi Feddern: Goodbye hard drive - How flash memory is gradually conquering the PC . In: c't magazine for computer technology . No. 21 , 2007, p. 100 ( online ).