Intel MCS-51

| << Intel 8051 >> | |

|---|---|

Intel P8051 |

|

| Production: | 1980 to 1990s |

Producers:

|

|

| Processor clock: | 12 MHz |

| Instruction set : | 8 bit |

| Base: | 40-pin DIP |

MCS-51 is the name of a 1980 by Intel introduced family of 8-bit - microcontrollers . With a microcontroller, all parts of a computer system ( processor , program memory, data memory and input / output units) are ideally combined in a single module. The MCS-51 family succeeded the MCS-48 family. At the beginning it had only three members with the designations 8051, 8031 and 8751. With the 8031 the ROM is in an external component, whereas with the 8051 and 8751 it is in the component itself - either in a mask-programmed ROM (8051) or in a EPROM (8751). In 1983 the variants 8052, 8032 and 8752 were introduced, each with double ROM and RAM and an additional timer. The family was initially manufactured in NMOS technology , and after a few years also in today's standard CMOS technology .

Intel has licensed the MCS-51 CPU core to many semiconductor manufacturers and thus created the basis for a manufacturer-independent industrial standard. MCS-51-compatible microcontrollers have long been available not only from Intel, but also from Analog Devices , Atmel , Infineon , Maxim / Dallas, Oki , NXP Semiconductors ( Philips ), Silicon Laboratories , Texas Instruments and the like. v. a. manufactured.

The SDK-51 was offered by Intel as a development system.

structure

The MCS-51 family has produced a great many members, including a. the Siemens 80C517 . They have the following things in common:

- 8-bit processor core with a uniform instruction set

- At least 128 bytes of internal RAM

- External RAM and ROM

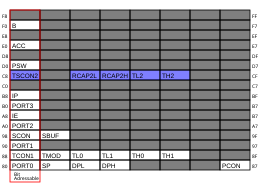

- A uniform addressing model for so-called Special Function Register (SFR)

- Full duplex UART

- 5 interrupt sources

- 2 interrupt priorities

- Various timers

Due to the different command lengths from one to three bytes and the different execution times for a command, it is clearly a CISC architecture.

An instruction cycle corresponds to the originally developed by Intel structure one to three machine cycles (multiplication and division need 4). One machine cycle corresponds to 12 clock cycles. On the other hand, the variants of the MCS-51 that are common today usually get by with only 2 clock cycles per machine cycle. This means that commands can be processed much faster with the same clock frequency.

A special feature of this processor is the bit processor, which allows quick and easy bit manipulation in the bit addressable area.

Due to the widespread use of this processor family and the associated large software libraries, there is also a large number of synthesizable MCS-51 implementations. These are freely available as so-called IP cores in a hardware description language such as VHDL and in the source code . They are suitable for use in FPGAs and application-specific integrated circuits (ASICs). Typical application examples are USB controllers such as those used in printers or interface adapters . MCS-51 microcontrollers are integrated into these to control the various protocols.

variants

The MCS-51 series includes the following well-known microcontrollers (all memory information is in bytes):

| NMOS and CHMOS variants | ||||||||

| Type | ROM internal |

RAM internal |

16-bit timer |

UART | ext. IRQ sources |

comment | NMOS | CHMOS |

|---|---|---|---|---|---|---|---|---|

| 8031 | - | 128 | 2 | 1 | 2 | x | x | |

| 8032 | - | 256 | 3 | x | x | |||

| 8051 | 4096 | 128 | 2 | mask programmable ROM | x | x | ||

| 8052 | 8192 | 256 | 3 | mask programmable ROM | x | x | ||

| 80C54 | 16384 | 256 | 3 | mask programmable ROM | - | x | ||

| 80C58 | 32768 | 256 | 3 | mask programmable ROM | - | x | ||

| 8751 | 4096 | 128 | 2 | EPROM as OTP or with UV window | x | x | ||

| 8752 | 8192 | 256 | 3 | EPROM as OTP or with UV window | x | x | ||

| 87C54 | 16384 | 256 | 3 | EPROM as OTP or with UV window | - | x | ||

| 87C58 | 32768 | 256 | 3 | EPROM as OTP or with UV window | - | x | ||

| 89C52 | 32768 | 256 | 3 | Flash memory | - | x | ||

| 8044 | 4096 | 192 | 2 | ? | RUPI ™ -44 (Remote Universal Peripheral Interface), mask-programmable ROM | x | - | |

| 8344 | - | 192 | 2 | RUPI ™ -44 (Remote Universal Peripheral Interface) | x | - | ||

| 8744 | 4096 | 192 | 2 | RUPI ™ -44 (Remote Universal Peripheral Interface), EPROM as OTP or with UV window | x | - | ||

In addition, there are extended MCS-51 microcontrollers from various companies, e. B. developed by Siemens (now Infineon ) and manufactured using NMOS technology:

| Type | ROM internal |

RAM internal |

comment |

|---|---|---|---|

| SAB 80515 | 8192 | 256 | Manufacturer: SIEMENS, 3 × 16-bit timer, 1 UART, 2 external interrupt sources, PWM , 8-way A / D converter, mask-programmable ROM |

| SAB 80535 | - | 256 | 3 × 16-bit timer, 1 UART, 2 external interrupt sources, PWM, 8-way A / D converter |

The CMOS variants of the Siemens MCS-51 series are functionally identical, but not all variants are pin-compatible.

Other modern MCS-51-compatible microcontrollers, which are manufactured in CMOS technology with flash memory and usually have faster command processing, more memory or special interfaces:

| Manufacturer | Type | Flash internal |

RAM internal |

comment |

|---|---|---|---|---|

| ATMEL | AT89C2051 | 2048 | 128 | Only 20 pins, no external data / address bus, 2 × 16-bit timers, 1 UART, 1 comparator, flash memory |

| ATMEL | AT89C4051 | 4096 | 128 | |

| ATMEL | AT89C51ED2 | 16384 | 256 | Up to 6 ports (depending on the housing size), 1792 bytes internal MOVX-SRAM, RS232 boot loader in ROM, 2 KBytes internal data EEPROM, 3 × 16-bit timer, 1 UART, 1 comparator, 2 data pointers, PWM , SPI, flash memory |

| MAXIM / DALLAS | DS89C430 | 16384 | 256 | 1 clock cycle / command, max. 33 MIPS at 33 MHz, 1 KB internal MOVX-SRAM, RS232 boot loader in ROM, 3 × 16-bit timer, 1 UART, 1 comparator, 2 data pointers, flash memory |

| MAXIM / DALLAS | DS89C450 | 65536 | 256 |

Storage organization

The stack is always freely definable in the internal RAM. The byte order is little endian first. In its original form it is a Harvard architecture , but many newer MCS-51 developer boards have a modified Harvard architecture. With this architecture, part of the XRAM (extended data RAM) is mirrored in the program memory using an address decoder . This enables a terminal software running mostly from ROM, e.g. B. to load incoming software into the program memory via the serial interface and to execute it after the transfer.

Data storage

The 4 register banks each contain 8 registers that can be addressed either as registers or via their address. The advantages of the registers over the "RAM for general use" are the shorter commands. Registers 0 and 1 can be used as 8-bit data pointers in the internal and external RAM. The response time to an interrupt can be shortened by clever use of the register banks, since the data does not have to be moved to the stack.

Since the upper RAM and the Special Function Register share the addresses, the type of addressing is used to differentiate. The upper RAM can only be addressed indirectly using register 0 and register 1, while the special function registers can be addressed using direct addressing.

During programming, the command differentiates between the extended RAM (extended data RAM or XRAM for short) and normal RAM. MOVresponds to the internal RAM, while MOVXthe XRAM responds. The XRAM can only be addressed indirectly, but linearly. In the early versions, the XRAM was always external, in newer versions it can be partially or fully integrated.

Due to the address bus width of 16 bits, up to 65536 bytes of XRAM are possible.

The special function registers or memory addresses of the XRAM are used by certain variants of controllers or controller boards for extensions of all kinds. As an an example:

- Further inputs and outputs

- 16-bit computing unit

- USB controller

- ...

This is particularly useful for the synthesizable MCS-51 implementations because the instruction set of the MCS-51 family is not changed, which means that compatibility with their development tools is maintained.

Program memory

Since the address bus is 16 bits wide, the external program memory can contain up to 65536 bytes. Either the internal or the external program memory can be used. Simultaneous operation is not possible.

With MOVC, the program can read from the program memory, which is helpful when implementing tables.

Ports

All ports can be operated as inputs or outputs, whereby ports 1 to 3 have an internal pull-up resistor. Port 0 is a real tri-state port that is used together with port 2 for external storage access. Port 0 is used in time division multiplex for outputting the lower address byte or input and output of the data. At the same time, the upper address byte appears on port 2.

RMW commands read the value from memory, while all other commands get the values from the pin.

Literature and data sheets

- J. Koch (arr.): The 8-bit microcontroller family 8051, 1. Features . Philips / Valvo, 1984. ISBN 3-87095-260-1

- J. Koch (arr.): The 8-bit microcontroller family 8051, 2nd instruction set . Philips / Valvo, 1984. ISBN 3-87095-261-X

- Microcomputer SAB 8051 command list . Published by Siemens AG, Components Division, Balanstrasse 73, 8000 Munich 80 (Order No. B / 2591)

- Andreas Roth: The Microcontroller Cookbook MCS51 , 6th edition, mitp Verlag, January 2002, ISBN 978-3-8266-0722-6

- R. Leicht: The great 51 application book . Franzis Verlag 2005, ISBN 3-7723-5419-X

- J. Walter: Microcomputer technology with the 8051 controller family . 3rd edition, Springer 2008, ISBN 978-3-540-66758-2

- M. Baldischweiler: The Keil C51 Compiler , ISBN 3-9804331-8-8

- Intel MCS-51 ™ Family of Single Chip Microcontrollers User's Manual , January 1981

- Microcontroller Handbook , Intel Corporation 1984, Order number 210918-002

- 8-Bit Embedded Controllers , Intel Corporation 1991, Order number 270645-003

- MCS ® 51 microcontroller Family User's Manual , February 1994 Publication number 121517, Intel Corporation; PDF

- MCS-51 ™ Macro Assembler User's Guide , Publication number 9800937, Intel Corporation

Individual evidence

- ^ John Wharton: An Introduction to the Intel ® MCS-51 ™ Single-Chip Microcomputer Family , Application Note AP-69, May 1980, Publication number 121518, Intel Corporation; PDF ( Memento of the original from February 24, 2013 in the Internet Archive ) Info: The archive link was inserted automatically and has not yet been checked. Please check the original and archive link according to the instructions and then remove this notice. .

- ^ John Wharton: Using the Intel® MCS-51 ™ Boolean Processing Capabilities , Application Note AP-70, May 1980, Publication number 203830-001, Intel Corporation; PDF .

- ↑ a b Intel's CPU family trees ( Memento from March 14, 2011 in the Internet Archive )

- ↑ Complete implementation of an MCS-51 microcontroller in VHDL under the GNU Lesser General Public License .

- ↑ a b c d e f MCS ® 51 8-Bit Control-Oriented Microcontroller

- ↑ a b 8XC51FX CHMOS single-chip 8-bit microcontrollers

- ↑ a b c d e f 8XC52 / 54/58 CHMOS SINGLE-CHIP 8-BIT MICROCONTROLLER

- ↑ a b c 8044AH / 8344AH / 8744H High Performance 8-Bit Microcontroller With On-Chip Serial Communication Controller

- ↑ M8744H RUPI ™ -44: Remote Universal Peripheral Interface

- ↑ J. Koch: The 8-bit microcontroller family 8051 , volume 1 (properties), Valvo / Boysen + Maasch, October 1984, p. 21ff, ISBN 3-87095-260-1