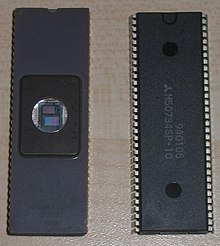

MOS Technology 6502

The computer chip MOS Technology 6502 is an 8- bit - microprocessor from MOS Technology, Inc. , which in 1975 came on the market. Due to its simplicity and, above all, its very low price compared to the then established Intel and Motorola processors with high performance, it was used in many home computers (e.g. the Commodore VC-20 and its predecessor PET 2001 , the Atari 800 , Apple I , Apple II and BBC Micro ), numerous chess computers (e.g. the Mephisto Polgar with 5 or 10 MHz), used in the world's first skat computer Skat Champion and many peripheral devices. The processor was developed under the direction of Chuck Peddle .

Other members of this processor family were also very successful, such as the 6510 , part of the Commodore 64 , and the 6507 in the Atari game consoles. The main competitor at the time was the Zilog Z80 . B. in the Sinclair and Schneider computers as well as in many CP / M computers.

General

The design of the 6502 was based on that of the Motorola 6800 (not to be confused with the younger Motorola 68000 ). The instruction set is similar, but instead of a 16-bit index register , two 8-bit index registers are used, the value of which is added to a 16-bit address specified in the memory (also in the program code). That's why 6502 programs have a different style: For arrays that are larger than 256 bytes, additional programming effort must be made. On the other hand, manipulating 8-bit values on an 8-bit microprocessor is much faster.

Unlike the 16-bit registers of the 6800 or the Z80, which represent an absolute address, the 8-bit registers of the 6502 only represent an array index (in the narrow range of values from 0 to 255), and in some cases a single 8-bit increment or decrement command both counting the addresses and setting the condition for the loop abort at index = 0, which leads to compact and fast loops. However, the simpler set of instructions means that 6502 programs normally require significantly more memory than the same 6800 or Z80 programs; In addition, standards-compliant compilers for higher programming languages such as Pascal or C are much more difficult to implement on the 6502 and generate slower code than on other 8-bit processors. The main reason for this is the size of the hardware stack memory (see below) in the 6502, which is limited to 256 bytes, so that the large stack memory required for most modern high-level languages has to be simulated by software. In order to keep the chip area small, the 6502 has only one battery in contrast to the two batteries A and B in the 6800.

The 64 KB address space of the 6502 is divided into several areas, which are mainly based on the page limits , where the high byte of the 16-bit address changes its value:

- Zeropage (first 256 bytes), it serves practically as a register bank , its contents can be accessed particularly quickly, and two consecutive bytes can be used as 16-bit values for various indirect addressing types.

- The following 256 bytes serve as stack memory (stack page), which grows down from the top. When the used stack depth is kept under control, the lower areas of this page are often used for other purposes (like normal RAM).

- The whole remaining area except for the last 6 bytes can be customized for RAM, ROM, or memory mapped I / O can be used. The 6502 dominates, unlike, say, the Z80, no Isolated I / O .

- The last 6 bytes (FFFA 16 –FFFF 16 ) contain three pointers for (starting from the top) the "normal" interrupt (IRQ), the reset vector and the non-maskable interrupt (NMI). In order for these memory locations to contain sensible values during a reset, the operating system or firmware ROM is usually located at the upper end of the address range, while the RAM starts at address 0. With a hardware reset, the program found from memory address 0 is not simply processed, as is the case with many other processors, but the vector from the two addresses FFFC 16 -FFFD 16 is copied into the program counter and then the software is processed from this point on.

Technically, the 6502 was quite innovative:

- In contrast to other microprocessors of the time, it already contained an integrated clock generator, which only required an external clock signal and which itself generated two non-overlapping clock signals (φ1 and φ2) for other circuits.

- It was the first microprocessor with a rudimentary (two-stage) pipeline architecture ; H. if only internal switching steps were necessary for a command, the next command could already be fetched from the memory at the same time. A real pipeline with overlapping read and write accesses of several commands did not yet exist.

- Its instruction set can - at least in comparison to its direct competitor, the Intel 8080 - be viewed as "almost orthogonal ".

- Instead of microcode , it contained a PLA whose 130 outputs directly took over the internal process control depending on the machine language command and the internal clock signal. As a result, the number of clock cycles required per command could be kept significantly smaller than with the competition.

Variants of the 6502 processor were used (as of 2008) in the following devices:

- Processor core of the Mitsubishi / Renesas microcontrollers (38000/740 Series)

- VMC Scal from Micronas Intermetall (used in automotive and television technology)

- Pocket calculators like HP 35s

- Controllers in various PC keyboards

- Controller in digital picture frame (Sitronix St2205)

The cc65 is often used as a cross compiler .

Technical specifications

- Technology: NMOS , HMOS , CMOS

- Number of transistors: approx. 3510

- Clock frequency: traditionally 20 kHz to 4 MHz; CMOS version: 0 to 14 MHz

- Clock cycles per command: 2 to 7

- Address space: 64 Kbytes , with no separate I / O address space (such as with the Intel 8080 ), i. H. All I / O via memory mapped I / O realized.

- Address bus width: 16 bits

- Data bus width: 8 bits

- Interrupts: an NMI , an IRQ , as well as software interrupt via BRK command. In terms of circuitry, the reset of the 6502 is also implemented as an interrupt. The interrupt vectors are at fixed addresses at the end of the address space (FFFA 16 to FFFF 16 ).

- Commands: traditional 56, CMOS version: 70

- Addressing types : traditional 13, CMOS version: 16

- Byte order : little endian

-

Register :

- Accumulator , 8 bit

- 2 index registers (X and Y), 8 bits, actually these are offset registers: each of the registers is added to a 16-bit address (exception: addition to 8-bit zeropage address), depending on the Addressing type is in the machine command itself or in the zeropage .

- Stack pointer, 8 bits; the stack pointer (low byte) is expanded by a constant high byte (01 16 ) in order to generate a 16-bit address. The stack thus comprises 256 bytes in the address range from 0100 16 to 01FF 16 .

- Processor status register, 7 bit (flags: Carry, Zero, Interrupt Disable, Decimal, Break *, unused , Overflow, Negative)

- Command counter, 16 bit

- The Zero Page (address range 00xx 16 ), because of its special, faster addressing species and their use in indexed addressing as a register bank or register file to be viewed

* Note: The break flag only exists on the stack after a BRK command, not in the processor itself. It has no set and test commands of its own and is also not processed by the PLP and PHP commands.

Instruction set

Examples of machine commands or their opcode and mnemonics in connection with different types of addressing.

| Opcode | Mnemonic | function |

|---|---|---|

$A9 |

LDA #$FF |

Loads (" L oa D ") the register " A kkumulator" with (255 decimal).

FF16 |

$AD |

LDA $C000 |

Loads the accumulator with the contents of the absolute memory address (49152 decimal).

C00016 |

$A1 |

LDA ($24),Y |

Loads the accumulator with the content of the memory address that results from adding the content of the Y register to the 16-bit number in the addresses and the contents. See zeropage , indirect addressing.

24162516 |

$8D |

STA $C000 |

Stores ( " ST ore") the contents of the A kkumulators (1 byte) in the memory address .

C00016 |

$6D |

ADC $C001 |

Adds (" AD d with C arry-Bit") the content of the memory address (1 byte) to the content of the accumulator (plus 1 if the carry bit is set).

C00116 |

$C9 |

CMP #$7F |

Compares (" C o MP are") the contents of the accumulator with the numerical value (127 decimal) and sets the flags accordingly.

7F16 |

$E4 |

CPX $C0 |

Compares the content of the register X with the content of the memory cell .

C016 |

$C0 |

CPY #$C0 |

Compares the content of register Y with the numerical value .

C016 |

$F0 |

BEQ $FC00 |

(" B ranch if result is EQ ual") Branches if the previous comparison resulted in equality (is determined on the basis of the flags). In this case the machine program would continue at address , otherwise with the next command that follows. The branch commands only allow relative addressing with a signed offset of ± 127, i.e. with a single byte as an argument.

FC0016BEQ |

$D0 |

BNE $FC00 |

(" B ranch if result is N ot E qual") Branched if the comparison resulted in an inequality. |

$E8 |

INX |

(" IN crement X ") Increases the content of register X by 1. |

$88 |

DEY |

(" DE crement Y ") Decreases the content of register Y by 1. |

$20 |

JSR $FC00 |

( " J ump to S ub R outine") Jump to the subroutine (subprogram) to the address . The return address consists of 2 bytes and is placed on the stack.

FC0016 |

$60 |

RTS |

(" R e T urn from S ubroutine") Returns from the subroutine and continues with the command immediately after the last one executed JSR. The last return address on the stack is read out.

|

In assembler program texts of the 6502, the dollar and number signs as well as the brackets have the following meaning:

- $ - The value following the $ sign is a number in HEX . Without $, a decimal number is meant for digits and a symbolic constant for letters.

- # - The value following the # character is a number to be used directly (immediate) and not a memory address whose content is to be used. The character thus identifies another type of addressing, direct addressing.

- () - The memory address mentioned in brackets is not to be used directly, but in turn contains the intended memory address (indirect addressing , pointer ).

There are CMOS versions of the 6502 from different manufacturers that have an extended command set or other addressing types. These changes are likely to result in serious changes to the undocumented opcodes discussed below.

Undocumented opcodes

The 6502 is known for a number of commands that are not in the official documentation, but still exist and work. Colloquially, such commands were called “illegal opcodes”. Of the 256 possible opcodes , only 151 are actual commands. Of the remaining 105 undocumented codes, there are many that have functionality, and quite useful ones. Some assemblers support such commands, but there is no standard specification for naming them with mnemonics.

Data processing can be accelerated with a large number of undocumented opcodes, since they perform functions in just a few clock cycles that are otherwise only possible with several consecutive commands, which in total consumes considerably more clock cycles. However, this harbors the risk that such commands will not work equally on all CPUs produced or that a possible successor model will not be able to handle these commands at all. As a result, the program would no longer fulfill its function correctly or not at all.

Other unofficial functions of the 6502 are (mnemonics only unofficial):

| Opcode | Mnemonic | function |

|---|---|---|

$AF |

LDA-LDX $C000 |

Loads the accumulator and the register X equally with the contents of the absolute memory address in hexadecimal (49152 decimal).

C00016 |

HALT |

Stops the processor. Actually leads to a crash that can only be fixed by a reset. | |

NOP |

" N o OP eration". Command without function. As with most opcodes, there are also several for NOPwith different types of addressing, which, however, only differ effectively in the number of bytes used and clock cycles used. NOPis used to skip several bytes in the program.

|

|

ASL-ORA |

Executes ASLon the data and ORs the contents of the accumulator with the result.

|

|

AND #n‑MOV b7‑>Cy |

Performs an AND operation of the data with the contents of the accumulator and takes over the seventh bit of the accumulator as the new state for the carry flag. | |

ROL-AND |

Executes ROLon the data and ANDs the contents of the accumulator with the result.

|

|

LSR-EOR |

Executes LSRwith the data and combines the contents of the accumulator EXCLUSIVE-OR with the result.

|

|

ROR-ADC |

Executes RORon the data and adds the result to the contents of the accumulator.

|

|

STA-STX |

Should write the contents of the accumulator and the register X simultaneously to a memory address. Because both register contents are on the bus line at the same time, this effectively results in an AND operation of the two registers, which is written to the specified memory address. Also known as SAX. | |

TXA-AND #n |

Transfers the content of register X into the accumulator and combines the new content of the accumulator AND with #n. | |

LDA-LDX |

Loads the same data into the accumulator and into the register X. Some addressing types can be unstable, i.e. the instruction can be linked with unpredictable side effects. Also known as LAX. | |

DEC-CMP |

Decreases the value of the data by 1 and compares the result with the contents of the accumulator. | |

INC-SBC |

Increments the value of the data by 1 and subtracts the result from the contents of the accumulator. |

Clock variants of the MOS 6502

- MOS 6502

- Clock frequency: ≈1 MHz

- Used in the Commodore PET and -CBM models PET 2001 to CBM 8296 as well as in the VC20 and the VC1540 and VC1541 floppy drives

- Used in the Apple I , Apple II , Apple II + , and the not expanded Apple IIe

- Used in the Ohio Scientific Superboard II

- Used in the computers of the Ohio Scientific Challenger series

- MOS 6502A

- 2 MHz clock

- Used in the Apple III

- Used in the 8-bit Atari home computers 400 and 800 with 1.79 MHz (1.77 MHz in PAL mode)

- Used in some Commodore floppy drives, e.g. B. VC1570 , VC1571 and VC1581

- Used in the Skat Champion , the world's first skat computer from Novag Industries Ltd.

- MOS 6502B

- 3 MHz clock

- MOS 6502C

- 4 MHz clock

Inferred designs

- Ricoh 2A03

- Ricoh 2A07

- PAL version of the 2A03

- Changed frequency dividers and color tables

- Used in European and Australian NES versions

- YM-2002

- Developed by Yamaha

-

Sun Plus SPLB31A

- Embedded version of the 8502 with integrated display and I / O controllers

- Used in the HP 35s

- Renesas 38000

- Microcontroller family from Renesas Technology with a 740 core. See 740

- M50740

- Mitsubishi microcontroller with 65C02 core

- SM630 ( СМ630 )

- Bulgarian clone of the 6502 from KMT-Pravets

- Ricoh 5A22

- HuC 6280

- Developed by Hudson Soft based on the 65SC02 design

- incl. MMU (2 MB addressable)

- 6-channel PSG

- Used in NEC's PC engine

- MOS 6500/1

- 2 KB ROM, 64 bytes RAM and a UART integrated

- Used in the Commodore plotter 1520

- MOS 6501

- Housing and signal compatible (not software compatible) to the Motorola 6800 (without the internal clock generator of the 6502 mentioned above). Had to be discontinued following a Motorola patent infringement lawsuit .

- 6502B

- 6502C ("SALLY")

- Custom design of the MOS 6502, designed and manufactured for ATARI

- HALT signal on pin 35

- second R / W signal on pin 36

- up to 1.79 MHz clock rate (1.77 MHz in PAL mode)

- Used in Atari's 8-bit home computer series XL and XE as well as in the Atari 5200 and Atari 7800 game consoles

- W65C02

- Developed by Western Design Center (WDC)

- CMOS technology

- Additional commands and addressing modes

- No illegal opcodes

- Some instructions require fewer or more clock cycles than in the 6502 under certain conditions

- Used in the expanded Apple IIe and Apple IIc and in some early accelerator cards for 6502 systems

- Manufactured by WDC, Rockwell International , Synertek, Sanyo, and others.

- The WDC variant is not pin-compatible with the 6502

- 65SC02

- Slightly restricted instruction set (no bit instructions, real subset of the 65816 ) compared to the 65C02

- Used in the Atari Lynx and Watara Supervision with 4 MHz clock

- Manufactured by GTE and CMD

- CSG 65CE02

- 1988 developed by the Commodore Semiconductor Group (CSG)

- Additional 16-bit RMW commands

- Relative jumps and subroutine calls with 16-bit offset

- Used in the Commodore 65 (as processor core of the 4510) and the Commodore A2232 7-Port Serial Card

- 3.54 MHz clock rate

- 65C102, 65C112

- Designed for multiprocessor operation, with the 65C112 serving as a slave

- Used in the BBC Micro and Commodore LCD

- MOS 6503, MOS 6505, MOS 6506

- 12 bit address bus (4 KB)

- MOS 6504, MOS 6507

- 13 bit address bus (8 KB), used e.g. E.g. in Commodore keyboards (Amiga 1000) and in floppy drives (Atari 1050) and printers (e.g. MPS 802 )

- 6507 used in the Atari 2600 with 1.19 MHz clock

- MOS 6509

- 20 bit address bus (1 MB) through internal bank switching

- Used in the Commodore PET II models ( CBM 500 , 600 and 700 ).

- MOS 6510

- DMA (AEC Pin 5) capable 6502 with an additional 8-bit I / O port, of which only 6 bits are brought out in the most common pin configuration.

- Different variants with the same designation (in the variant used in the C64, for example, only 6 bits of the port are available)

- Used in the C64 with 985 kHz (PAL version) or 1022 kHz (NTSC version) clock

- Used in the VC1551 with 2 MHz as 6510T

- Rockwell R6511Q

- Microcontroller with I / O ports, serial interface and RAM, from Rockwell

- Extended bit commands

- Rockwell R65F11

- Variant of the 6511 with integrated Forth interpreter (3 KB on-chip ROM)

- MOS 6512 to MOS 6518

- Variant of the corresponding 650x, but without a built-in oscillator.

- 65C00 / 21, 65C29

- Multiply instruction

- from Rockwell

- 6570, 6571

- Used in Amiga keyboards

- UA6588F / 81489

- Used in Bit Corporation Gamate

- Manufactured by UMC and NCR

- 6702

- used only in the plug-in board of the Commodore SuperPET

- Renesas 740

- Microcontroller family from Renesas Technology (formerly Mitsubishi Electric )

- Based on the 65C02

- more than 100 variants

- up to 60 KB ROM / PROM / Flash onchip

- up to 2 KB RAM onchip

- extended instruction set

- multiplication

- division

- Extended bit commands

- Stop / Wait

- New addressing types

- Transfer (memory memory commands)

- Special Page

- Bit relative

- Up to 17 MHz

-

MOS 7501

- CPU in HMOS technology that is command-compatible with the 6502

- 8-bit I / O port (only 7 lines led to the outside)

- Maximum clock: 2 MHz

- Used in the Commodore 16 and Plus / 4

- MOS 8500

- 6510 in HMOS technology

- MOS 8502

- 6510 switchable to 2 MHz

- 7-bit I / O port

- Used in the C128

- W65C134S

- Developed by Western Design Center (WDC)

- Microcontroller that u. a. a W65C02S-CPU, 4096 bytes ROM, 192 byte RAM, four 16-bit timers and a UART integrated on the same chip

- Maximum clock: 8 MHz

- W65C802

- Developed by Western Design Center (WDC)

- Variant of the 65816 , which is pin-compatible with the 6502, therefore address space like this only 64 KB

- Intended for the direct exchange of the 6502 in already existing circuits

- Up to 16 MHz

-

W65C816S

- Developed by Western Design Center (WDC)

- Used u. a. in Apple IIgs , Nintendo SNES (as Ricoh 5A22 ), most of the acceleration cards for 6502 computers

- 16-bit register and ALU

- 24-bit address bus (16 MB)

- Up to 24 MHz

- Compared to the 6502, it takes one cycle longer for many commands because of the additional address byte

Trivia

- The fictional robot Bender from the animated series Futurama has a 6502 processor as a CPU (Season 2 Episode 4 - The Party with Slurm McKenzie).

- In the movie Terminator (1984), a 6502 assembler program is shown from the Terminator's point of view (presumably from the Apple IIe ). Furthermore, the result of the checksum program Key Perfect (version 4.0), which was published in Nibble magazine , is displayed.

- According to Heise, the 65C02 version of the processor is available again (January 26, 2012).

- For this processor, a simulation was created on its transistor level in software and in hardware on a circuit board measuring approximately 30 × 40 cm ("MOnSter6502").

literature

- Brian Bagnall: On The Edge: The Spectacular Rise and Fall of Commodore. ISBN 0-9738649-0-7 .

- Brian Bagnall: People's Computer - Rise and Fall of the Computer Pioneer Commodore . Ed .: Winnie Forster, Boris Kretzinger. Gameplan, Utting am Ammersee 2011, ISBN 978-3-00-023848-2 (American English: On the Edge: the Spectacular Rise and Fall of Commodore . Translated by Winnie Forster, Boris Kretzinger).

- Ekkehard Flögel: Programming in machine language with the 6502. ISBN 3-921682-61-4 .

- Lance A. Leventhal: 6502. Programming in ASSEMBLER. ISBN 3-921803-10-1 .

- Rodnay Zaks: Programming the 6502. Now also with 6510, 65C02, 65SC02. ISBN 3-88745-600-9 .

Web links

- 6502.org - Information about the 6502 processor

- CCOM - Commodore Computer Online Museum

- 6502 page from Homecomputermuseum.de

- 6502 processors and variants: Pictures and descriptions on cpu-collection.de

- CPU-World - overview of the different manufacturers

- visual6502.org : microscopy images and simulator with single transistors

- Easy 6502 : 6502 assembler tutorial with integrated emulator

Individual evidence

- ↑ Transistor count in 6502

- ↑ Reverse Engineering the 6502 ... with 3,510 transistors

- ↑ Overview of 6502 assembler commands on C64-Wiki.de

- ↑ Full 6502 Opcode List Including Undocumented Opcodes , JG Harston, November 25, 1998

- ↑ InfoWorld , Volume 5, No. 12 (March 21, 1983), InfoWorld Media Group, Inc .; P. 41. ISSN 0199-6649.

- ↑ Available again: the 6502 microprocessor

- ↑ visual6502.org

- ↑ monster6502.com