System-on-a-chip

Under System-on-a-chip ( SoC , dt. A system on chip ), and system-on-chip , refers to the integration of all or a large part of the functions of a programmable electronic system on a chip ( The ), so an integrated circuit (IC) on a semiconductor - substrate , also called monolithic integration. Due to the frequent use of silicon as a substrate material, it is also referred to as system-on-silicon (SoS). A system is a combination of different elements (logic circuits, clocking, independent start-up, microtechnical sensors , etc.) that together provide a certain functionality, for example an acceleration sensor including evaluation electronics. SoCs are usually used in embedded systems .

While systems initially consisted of a microprocessor or microcontroller IC and many other ICs for special functions that were soldered onto a circuit board, the integration density possible today allows almost all functions to be combined on a single IC. Digital, analog and mixed-signal functional units are integrated. The main advantages are cost savings, lower energy consumption or power loss and extensive miniaturization. Today, for example, in cell phones, the digital function, possibly with the exception of the memory, is implemented on an IC. The interfaces, for example to the keyboard, the SIM card or the display, are already included on this IC.

A similar technique for achieving high integration densities of components with very different technologies is the so-called system-in-package (SiP). Several chips are combined in one housing.

operation area

SoCs are used, among other things, in mobile devices such as gadgets and data recording devices and in control and automation technology (e.g. washing machines, automotive electronics, industrial automation). Usually there are many different interfaces to use (sensors, actuators, networks, buttons, displays) and the quantities are large. The integration of the functions that were previously distributed over several components or even several circuit boards can also increase the failure and functional safety , especially if various measures for error detection are integrated that could not be implemented with discrete components in a marketable manner. For applications that generate fewer quantities, such as in medical devices or avionics , specially adapted SoCs are rarely used, but many of the integrated modules often remain unused.

Design process

Nowadays, SoCs are usually not completely redeveloped, but the designs are based - at least in part - on existing or purchased components, so-called IP cores . These are, for example, macros for complete CPU cores or coprocessors - for example as hardware accelerators for encryption or graphic calculations. These are also peripheral blocks for the implementation of memory , Ethernet , Bluetooth or other interfaces, or even complete memory units including their management.

Many standard components are included free of charge in EDA tools from chip manufacturers in proprietary form. Other components can be obtained from the chip manufacturer or other IP suppliers such as B. ARM , Transmeta or smaller often very specialized development companies are licensed. Often, such IP cores can be generated using parameters adapted to the intended use, for example in the form of the pipeline length, the cache size or the bus bit widths.

Other required components of a SoC, for example, have already been developed in earlier projects and, ideally, can be used directly - or changes have to be made; at best, parameterization of the IP cores is sufficient. Another possibility is to use “free hardware”. More and more open source projects are emerging in the hardware sector (e.g. on OpenCores.org ), which are often still in the development stage. Anything that may be missing here must be developed by the user himself or have it developed.

The transitions between what is implemented in software and what is implemented in hardware are increasingly fluid depending on the application - see Software Defined Radio (SDR).

Debugging Interface

Usually SoCs have a debug interface (English interface ). This is often a simple RS-232 interface, but USB is also increasingly being used here . Error messages and general information can then be output during operation via this debug interface, for example on a terminal, that is to say a console application. In more complex environments, this function is often also performed by a JTAG interface. This is typically not only used to transmit error messages, but also to communicate with a hardware or software debug module in the SoC. Such a module allows the user, for example, to "stop" the SoC and execute the processing in the CPU core in single-step mode ("step-by-step") and, if necessary, change individual register values during this process or, for example, shorten a loop or add a jump command bypass.

Another application of this interface is the programming of programmable areas of a SoC, e.g. B. RAM , EEPROM , Flash or even individual circuit parts up to the entire SoC design (only in an FPGA or similar). In most cases, additional external modules are attached to the same JTAG interface as a "chain" and are addressed via a so-called boundary scan .

Components

bus

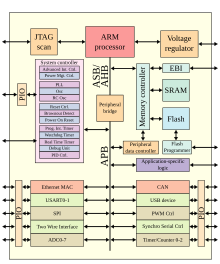

The system is connected internally via one or more buses. A hierarchical or at least segmented bus system is often used in more complex SoCs. This typically consists of a fast system bus , a slower peripheral bus and a register or control bus . Sometimes, however, fast peripheral units are also connected directly to the system bus. A bridge mediates between the system bus and the peripheral bus. Furthermore, every bus with several masters requires an arbiter . A proprietary but particularly fast processor bus is often used for the particularly important connection between the processor and his or her cache (s) or a small local memory. An example of this is the Xilinx LMB .

AMBA from Arm (Busse: AHB or ASB / APB), CoreConnect from IBM (Busse: PLB / OPB / DCR) or, more recently, the WishBone from Silicore / OpenCores.org are strongly represented as system bus in SoCs . Bus widths of 32 to 128 bits are widespread today. With powerful SoCs, there is often a DMA controller on the system bus to relieve the CPU of memory access.

The specifications of these buses are all physically designed for implementation in ASICs ( application-specific integrated circuits ) and / or FPGAs ( Field Programmable Gate Array ) and otherwise differ greatly from common system buses such as PCI - for example, due to the fixed system structure in general no plug and play used.

Clock

Function groups are included as clock generators and timers, which emit pulses at a specific frequency. These will be simple physical oscillators and other electronic functions for stabilizing the clock rate, which are required for sequence control and, if necessary, synchronization.

A real-time clock (physical clock) receives or measures and counts a physical time locally and can also be included. For this purpose, precise physical transducers are usually arranged externally to the SoC.

In a broader sense, apart from the clock generator and the real-time clock, the clock generator also contains special power-saving wake-up circuits that keep or update a time even after the system has been switched off. The clock (s) then also control the standby state or sleep mode .

processor

A SoC usually consists of a processor , which is connected to memory and other peripherals via a bus system . This processor can be either a very simple 8-bit microcontroller or a very powerful multicore CPU . Multiprocessor systems are also possible.

Depending on the performance, application requirements and other criteria such as power consumption, size and price, the SoC may only have a small internal memory in addition to its registers, or (usually in addition) one or more significantly larger external memories. This can be, for example, SDRAM or flash memory . For this purpose, a memory controller , which provides a corresponding interface for the memory, is usually attached to the system bus .

More processors

In order to relieve the actual main processor of the SoC, specialized processors are also included, depending on the application. These can, for example, be processors for digital signal processing ( DSPs ) or, for example, encryption / decryption units or other hardware accelerators such as physics accelerators . For this purpose, individual calculations or only parts of them can be outsourced. These are either completely taken over by the coprocessor , or the main processor only passes on individual, particularly computationally intensive commands. These are then possibly no longer executed as software on a general purpose CPU or DSP, but implemented directly in hardware. This is common practice, at least in FPGAs and ASICs, and is therefore directly supported by the EDA tools. Many modern FPGAs such as Virtex4 / 5 or StratixII / III also contain so-called DSP macros, with which so-called MAC commands can be executed very quickly in many parallel paths .

Storage

The memory in a SoC is used either to store and execute the program (program memory) or to store and process data (data memory). If the memory is a cache , it is often implemented in two separate memories as a Harvard architecture . Normal RAM , on the other hand, is usually implemented in a Von Neumann architecture . In terms of storage technology, it is mostly fast SRAM internally , while external storage, which is connected via a memory controller, is usually slower but cheaper DRAM or Flash .

Periphery

Which other peripheral units are integrated depends very much on the actual application, but of course also on many other factors such as the criteria mentioned for the processor type. These peripheral blocks are usually not attached directly to the system bus, but rather to a separate peripheral bus via a so-called bridge. This is usually clocked much slower, but meets the requirements of most peripherals. Thus, in addition to some other positive effects, the capacitive load on the system bus is primarily reduced, and this can be clocked faster, which of course only helps until the CPU actually has to wait for a peripheral unit; then normally both buses are busy without transmitting anything. In addition, a peripheral bus facilitates the development of simpler components, since the integration of this type of bus, in contrast to the system bus, is usually much easier and, due to its often smaller bit width and slower clock rate, has significantly lower requirements.

Depending on the type and number of peripheral blocks and the purpose of the SoC, it sometimes contains a dedicated interrupt controller . In simple, smaller or particularly inexpensive systems, however, such a controller is often dispensed with; the software must then determine the interrupt source. Progressive interrupt controllers not only offer many channels for assigning the interrupts, but also offer channels with different interrupt priorities. This is important when real-time requirements are made in parts of the system that cannot be solved easily or sometimes not at all with interrupts, since interrupts cannot be foreseen. This problem can often be solved through intelligent prioritization.

There are often far more peripheral modules than are used in a specific application. Less of the external connections remain unused, as these can often be assigned to different modules in a programmable manner. In some cases, the clock can be switched off for individual modules and the voltage can even be switched off for groups of modules in order to reduce power consumption.

graphic

Many SoCs also contain a graphics processor, which is used to control one or more displays. In a classic PC, for example, a separate graphics card or a graphics core (GPU) integrated in the chipset is responsible for this (so-called hardware acceleration ). Due to the trend towards ever increasing integration, large CPU manufacturers such as AMD / ATI, Intel and VIA / Nvidia have been planning to manufacture CPUs with integrated GPUs for several years . While some embedded systems place very high demands on the graphics output (game consoles, Blu-Ray / DVD players, imaging devices for medical technology or the military), in other cases LCDs or a few LEDs are often sufficient for status output. Depending on the application, graphical output can be dispensed with entirely.

The realization of the graphics capability is often made particularly difficult by particularly rigid specifications for maximum performance, the maximum chip area or by extreme price pressure if the goods are mass-produced.

Audio

Special audio cores can also be found in many SoCs. These are required, for example, in cell phones, MP3 and DVD players and similar multimedia devices. Depending on the requirements, number of items, financial possibilities, space restrictions, etc., external hardware audio codecs are often used, which are then only connected to the SoC internal bus via a relatively small IP block. If there are no particularly high demands on the audio quality, an AC'97 codec can be used, for example . Costs can only be saved with such external components for small quantities, since the development costs for an integrated or even self-developed solution often have a disproportionate effect.

Interfaces

SoCs typically communicate much more strongly with their technical environment than with an operator. Various interfaces are implemented for this, depending on the requirements. This is often done by integrating finished IP blocks which, depending on the speed and latency requirements, are connected to the internal system or peripheral bus.

For the operator, in addition to the audio and graphic interfaces already mentioned, a keyboard controller (e.g. for matrix keyboards, serial keyboards or touchpads) or a USB interface for corresponding devices can be used. For communication with other systems, serial interfaces such as B. USB , RS232 , CAN bus, LIN bus , MOST bus , ARINC 429 and Ethernet in question. Sometimes only the MAC layer is integrated in the SoC, but sometimes the PHY as well . Another possibility are parallel interfaces such as B. Centronics , Port-IO, IDE / CF etc.

System-on-a-programmable chip

SoCs are increasingly being implemented on programmable chips, so-called system-on-a-programmable chips . This is a combination of FPGA logic and other peripherals and CPUs . Both so-called hard cores (CPU cores present in the silicon parallel to the programmable FPGA logic) and soft cores (synthesizable CPU macros inserted into the FPGA source code) are used as processors. As hard cores there are, for example, PowerPC or ARM cores, as soft cores mostly manufacturer-specific processors such as the MicroBlaze from Xilinx or the NIOS II from Altera. There are also platform-independent synthesizable cores from ARM, Lattice and others, which are either sold commercially as IP cores or are available as open source. In this way, the required functions of a system can be optimally distributed among the resources offered.

This is not to be confused with solutions such as the PSoCs from Cypress or other companies, where only a classic microcontroller can be programmed, but not its ALU and the entire system with buses, memory and other peripherals.

The usual components of a SoC are:

- processor

- Graphics processor

- Sound chip

- Storage

- Internal units

- Timer

- counter

- Interrupt controller

- Watchdog timer

- Debug interfaces, e.g. B. JTAG

- Special processing units, such as B. in DSP SoCs

- Cryptography

-

Peripheral units and interfaces

- Keyboard controller, e.g. B. for matrix keyboards, serial keyboards or touchpads

- Graphic interfaces , e.g. B. for LVDS , LCD , VGA , DVI , MPEG , HD / SDMI

- Serial interfaces , e.g. B. USB , RS232 , CAN bus

- Parallel interfaces , e.g. B. Centronics , Port-IO

- Pulse width modulation , e.g. B. for DC-DC converter or motor control

- Modulators , e.g. B. for GSM coding, QAM , PSK

- Other interfaces, e.g. B. Ethernet, MAC or USB

- Analog-to-digital converter

Manufacturer

There are numerous offers for system-on-a-chip semiconductors on the market. Important providers for this are: (sorted alphabetically, not by size)

- ARM and Intel with the ARM architecture or the further development XScale (also Intel Quark or Intel Edison )

- Altera , Microsemi and Xilinx with various SoC platforms in FPGAs

- Broadcom with various communication chips

- Cypress Semiconductor Corporation for PSoC Programmable System on Chip

- Infineon and NXP with SoC ICs for mobile devices such as cell phones or xDSL modems

- LSI Logic with chips for network and storage products

- MIPS and licensees such as AMD with the AU1000 series

- Motorola / Freescale / NXP Semiconductors and IBM with various PowerPC derivatives

- Qualcomm ( Snapdragon ) for modern smartphone SoCs

- STMicroelectronics

- TDK-InvenSense with SoC-ICs for movement and position, picture and sound in the game controller , mobile phone and head-mounted display

- Texas Instruments with OMAP , DSPs and RF modules (e.g. ZigBee module µTiny)

literature

- Bashir M. Al-Hashimi: System-on-Chip: Next Generation Electronics . Institution of Engineering and Technology, 2006, ISBN 0-86341-552-0 .

- F. Kesel and R. Bartholomä: Design of digital circuits and systems with HDLs and FPGAs . Oldenbourg, 2006, ISBN 3-486-57556-2 . - Explains the design of digital circuits and SoCs based on FPGAs - VHDL example is a small microcontroller. Outlook for SystemC included (Note: Is not a VHDL beginners textbook!)

- Steve Furber: ARM computer architectures for system-on-chip design . Mitp-Verlag, 2002, ISBN 3-8266-0854-2 .

Web links

- SOCC - Annual international specialist conference of the IEEE with a focus on SoC research and development

- First system on chip. In: computerhistory.org.

- Altera SoC-FPGA Overview - Information on SoC-FPGAs from Altera

- Microsemi SoC-FPGA Overview - Information on SoC-FPGAs from Microsemi

- Xilinx SoC-FPGA Overview - Information on SoC-FPGAs from Xilinx

Individual evidence

- ↑ AMD develops integrated CPU-GPU chip. In: heise.de